TABLES

Table 1 − Super I/O Block Addresses ..........................................................................................................................24

Table 2 − Status, Data and Control Registers..............................................................................................................28

Table 3 − Internal 2 Drive Decode - Normal.................................................................................................................32

Table 4 − Internal 2 Drive Decode - Drives 0 and 1 Swapped .....................................................................................32

Table 5 − Tape Select Bits...........................................................................................................................................32

Table 6 − Drive Type ID ...............................................................................................................................................33

Table 7 − Precompensation Delays .............................................................................................................................34

Table 8 − Data Rates ...................................................................................................................................................34

Table 9 − DRVDEN Mapping0 .....................................................................................................................................34

Table 10 − Default Precompensation Delays...............................................................................................................35

Table 11 − FIFO Service Delay....................................................................................................................................36

Table 12 − Status Register 0........................................................................................................................................38

Table 13 − Status Register 1........................................................................................................................................39

Table 14 − Status Register 2........................................................................................................................................40

Table 15 − Status Register 3........................................................................................................................................40

Table 16 − Description of Command Symbols .............................................................................................................42

Table 17 − Instruction Set ............................................................................................................................................45

Table 18 − Sector Sizes...............................................................................................................................................52

Table 19 − Effects of MT and N Bits.............................................................................................................................52

Table 20 − Skip Bit vs Read Data Command...............................................................................................................52

Table 21 − Skip Bit vs. Read Deleted Data Command.................................................................................................53

Table 22 − Result Phase Table....................................................................................................................................54

Table 23 − Verify Command Result Phase Table ........................................................................................................55

Table 24 − Typical Values for Formatting.....................................................................................................................56

Table 25 − Interrupt Identification.................................................................................................................................58

Table 26 − Drive Control Delays (ms) ..........................................................................................................................59

Table 27 − Effects of WGATE and GAP Bits................................................................................................................61

Table 28 − Addressing the Serial Port..........................................................................................................................63

Table 29 − Interrupt Control Table ...............................................................................................................................65

Table 30 − Baud Rates ................................................................................................................................................71

Table 31 − Reset Function Table .................................................................................................................................72

Table 32 − Register Summary for an Individual UART Channel ..................................................................................73

Table 33 − Parallel Port Connector ..............................................................................................................................78

Table 34 − EPP Pin Descriptions .................................................................................................................................82

Table 35 − ECP Pin Descriptions.................................................................................................................................84

Table 36 − ECP Register Definitions............................................................................................................................85

Table 37 − Mode Descriptions......................................................................................................................................85

Table 38A − Extended Control Register.......................................................................................................................88

Table 39 − Channel Commands...................................................................................................................................90

Table 40 − Modified Parallel Port FDD Control ............................................................................................................93

Table 41 − FDC Parallel Port Pins ...............................................................................................................................93

Table 42 − PC/AT and PS/2 Available Registers .........................................................................................................95

Table 43 − State of System Pins in Auto Powerdown ..................................................................................................95

Table 44 − State of Floppy Disk Drive Interface Pins in Powerdown............................................................................96

Table 45 − RTC Configuration Registers .....................................................................................................................97

Table 46 − CMOS Run time Registers.........................................................................................................................98

Table 47 − RTC and CMOS RAM Address Map ..........................................................................................................98

Table 48 − RTC Register Valid Range.........................................................................................................................99

Table 49 − RTC Update Cycle Timing........................................................................................................................100

Table 50 − RTC Divider Selection Bits......................................................................................................................101

Table 51 − RTC Periodic Interrupt Rates ...................................................................................................................101

Table 52 − I/O Address Map ......................................................................................................................................108

Table 53 − Host Interface Flags .................................................................................................................................109

Table 54 − Status Register.........................................................................................................................................110

Table 55 − Resets......................................................................................................................................................111

Table 56 − GPIO Pin Functionality.............................................................................................................................115

Table 57 − General Purpose I/O Port Assignments ...................................................................................................117

Table 58 − GPIO Configuration Summary..................................................................................................................119

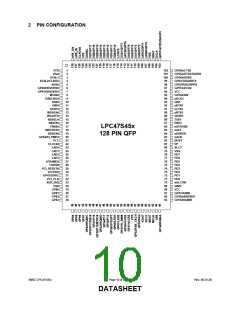

SMSC LPC47S45x

Page 6 of 259

Rev. 06-01-06

DATASHEET

SMSC [ SMSC CORPORATION ]

SMSC [ SMSC CORPORATION ]