2

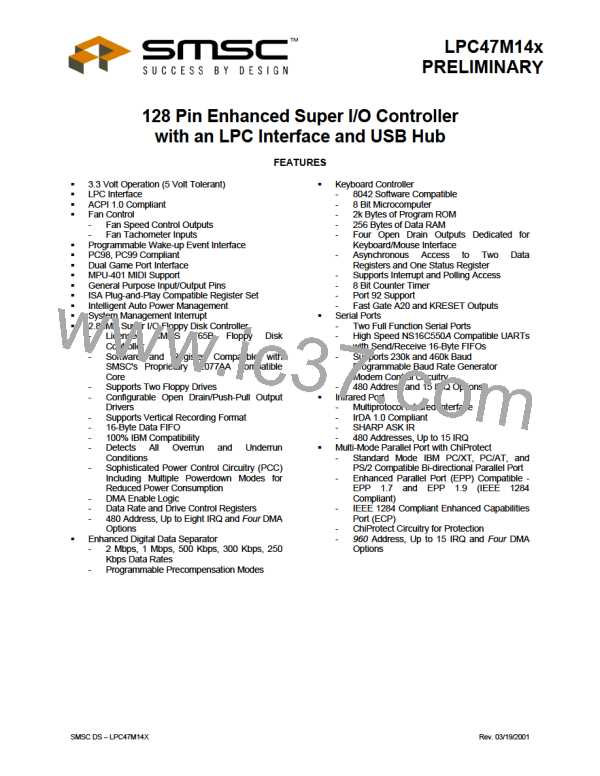

PIN CONFIGURATION

PIN #

NAME

PIN #

NAME

GP11 /J1B2

GP12 /J2B1

GP13 /J2B2

GP14 /J1X

PIN #

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

NAME

PIN #

97

NAME

GP54/nDSR2

GP55/nRTS2

GP56/nCTS2

GP57/nDTR2

VSS

1

GP40/DRVDEN0 33

GP41/DRVDEN1 34

VCC

2

nINIT

98

3

nMTR0

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

nSLCTIN

PD0

99

4

nDSKCHG

nDS0

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

5

GP15 /J1Y

PD1

6

CLKI32

GP16 /J2X

PD2

VSS

7

VSS

nDIR

GP17 /J2Y

PD3

USB +

8

AVSS

PD4

USB -

9

nSTEP

GP20/P17

PD5

PD1 +

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

nWDATA

nWGATE

nHDSEL

nINDEX

nTRK0

GP21/P16/nDS1

GP22/P12/nMTR1

VREF

PD6

PD1 -

PD7

PD2 +

VSS

PD2 -

GP24/SYSOPT

GP25/MIDI_IN

GP26/MIDI_OUT

GP60/LED1

GP61/LED2

GP27/nIO_SMI

SLCT

PD3 +

PE

PD3 -

nWRTPRT

nRDATA

GP42/nIO_PME

VTR

BUSY

nACK

PD4 +

PD4 -

nERROR

nALF

VTR

nPWREN1

nPWREN2

nPWREN3

nPWREN4

nUSBOC1

nUSBOC2

nUSBOC3

nUSBOC4

VTR

CLOCKI

LAD0

GP30/FAN_TACH2 83

GP31/FAN_TACH1 84

nSTROBE

RXD1

LAD1

VCC

85

86

87

88

89

90

91

92

93

94

95

TXD1

LAD2

GP32/FAN2

GP33/FAN1

KDAT

nDSR1

nRTS1

nCTS1

nDTR1

nRI1

LAD3

LFRAME#

LDRQ#

KCLK

PCI_RESET#

LPCPD#

GP43/DDRC

PCI_CLK

SER_IRQ

VSS

MDAT

MCLK

nDCD1

GP50/nRI2

VCC

GP51/nDCD2

GP52/RXD2

(IRRX)

GP53/TXD2

(IRTX)

ICLK

VSS

OCLK

IRRX2/GP34

IRTX2/GP35

GP36/nKBDRST

VCC

nStrp0

nStrp1

32

GP10 /J1B1

64

GP37/A20M

96

128

VSS

Note: The chip is part of a family of LPC chips (LPC47M13x, LPC47M14x, and LPC47M15x). The first 100 pins of

these chips are pin compatible, which adds more flexibility for the board designer. In addition, a board designed for

the LPC47M14x can also support the LPC47M13x with little or no changes made to the board design.

SMSC DS – LPC47M14X

Page 9

Rev. 03/19/2001

SMSC [ SMSC CORPORATION ]

SMSC [ SMSC CORPORATION ]