6.9.2

Extended Capabilities Parallel Port

ECP provides a number of advantages, some of which are listed below. The individual features are explained in greater

detail in the remainder of this section.

High performance half-duplex forward and reverse channel Interlocked handshake, for fast reliable transfer Optional

single byte RLE compression for improved throughput (64:1) Channel addressing for low-cost peripherals Maintains link

and data layer separation Permits the use of active output drivers permits the use of adaptive signal timing Peer-to-peer

capability.

Vocabulary

The following terms are used in this document:

assert:

When a signal asserts it transitions to a "true" state, when a signal deasserts it transitions to a "false"

state.

forward: Host to Peripheral communication.

reverse: Peripheral to Host communication

Pword:

A port word; equal in size to the width of the LPC interface. For this implementation, PWord is always

8 bits.

1

0

A high level.

A low level.

These terms may be considered synonymous:

ꢀ

ꢀ

ꢀ

ꢀ

ꢀ

ꢀ

ꢀ

ꢀ

ꢀ

PeriphClk, nAck

HostAck, nAutoFd

PeriphAck, Busy

nPeriphRequest, nFault

nReverseRequest, nInit

nAckReverse, PError

Xflag, Select

ECPMode, nSelectln

HostClk, nStrobe

Reference Document: IEEE 1284 Extended Capabilities Port Protocol and ISA Interface Standard, Rev 1.14, July 14,

1993. This document is available from Microsoft.

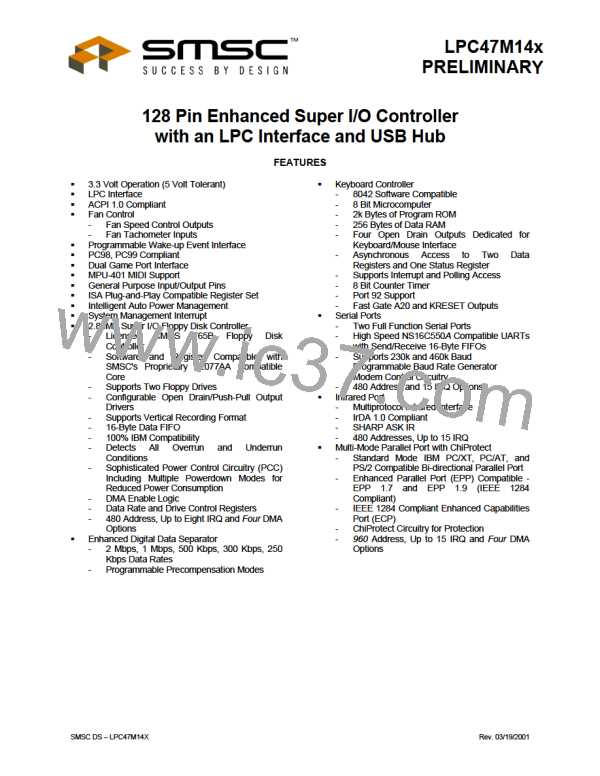

The bit map of the Extended Parallel Port registers is:

D7

PD7

D6

PD6

D5

PD5

D4

PD4

D3

PD3

D2

PD2

D1

PD1

D0

PD0

NOTE

data

ecpAFifo

dsr

dcr

Addr/RLE

nBusy

0

Address or RLE field

Select nFault

Direction ackIntEn SelectI

n

2

1

1

nAck

0

PError

0

nInit

0

0

autofd strobe

cFifo

ecpDFifo

tFifo

Parallel Port Data FIFO

ECP Data FIFO

Test FIFO

2

2

2

cnfgA

cnfgB

ecr

0

0

0

1

0

0

0

0

compress

intrValue

MODE

Parallel Port IRQ

Parallel Port DMA

nErrIntrEn dmaEn serviceIntr

full

empty

Note 1: These registers are available in all modes.

Note 2: All FIFOs use one common 16 byte FIFO.

Note 3: The ECP Parallel Port Config Reg B reflects the IRQ and DMA channel selected by the Configuration

Registers.

SMSC DS – LPC47M14X

Page 84

Rev. 03/19/2001

SMSC [ SMSC CORPORATION ]

SMSC [ SMSC CORPORATION ]