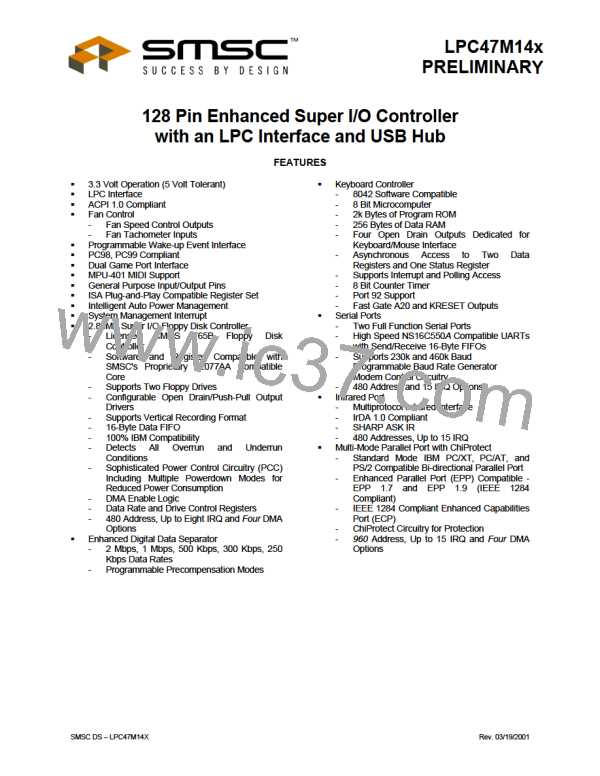

The operation of the GPIO ports is illustrated in FIGURE 8.

Note: FIGURE 8 is for illustration purposes only and is not intended to suggest specific implementation details.

Note: When the following functions are selected, the associated GPIO pins have bi-directional

functionality:

P12, P16, P17 and game port x-axis and y-axis inputs (J1X, J1Y, J2X, J2Y).

When a GPIO port is programmed as an input, reading it through the GPIO data register latches either the inverted or

non-inverted logic value present at the GPIO pin. Writing to a GPIO port that is programmed as an input has no

effect (Table 56)

When a GPIO port is programmed as an output, the logic value or the inverted logic value that has been written into

the GPIO data register is output to the GPIO pin. Reading from a GPIO port that is programmed as an output returns

the last value written to the data register (Table 56). When the GPIO is programmed as an output, the pin is

excluded from the PME and SMI logic.

Table 56 – GPIO Read/Write Behavior

HOST OPERATION

READ

GPIO INPUT PORT

LATCHED VALUE OF GPIO PIN

NO EFFECT

GPIO OUTPUT PORT

LAST WRITE TO GPIO DATA REGISTER

BIT PLACED IN GPIO DATA REGISTER

WRITE

The LPC47M14x provides 31 GPIOs that can directly generate a PME. See the table in the next section. The

polarity bit in the GPIO control registers select the edge on these GPIO pins that will set the associated status bit in

the PME_STS 2 register. The default is the low-to-high edge. If the corresponding enable bit in the PME_EN 2

register and the PME_EN bit in the PME_EN register is set, a PME will be generated. These registers are located in

the PME_BLK of runtime registers which are located at the address contained in the configuration registers 0x60 and

0x61 in Logical Device A. The PME status bits for the GPIOs are cleared on a write of ‘1’. In addition, the

LPC47M14x provides 19 GPIOs that can directly generate an SMI. See the table in the next section.

6.14.5 GPIO PME and SMI Functionality

The following GPIOs are dedicated wakeup GPIOs with a status and enable bit in the PME status and enable

registers:

ꢀ

ꢀ

ꢀ

ꢀ

ꢀ

ꢀ

GP10-GP17

GP20-GP22, GP24-GP27

GP30-GP33

GP41, GP43

GP50-GP57

GP60, GP61

The following PME status and enable registers for these GPIOs:

ꢀ

ꢀ

ꢀ

ꢀ

PME_STS2 and PME_EN2 for GP10-GP17

PME_STS3 and PME_EN3 for GP20-GP22, GP24-GP27

PME_STS4 and PME_EN4 for GP30-GP33, GP41, GP43, GP60 and GP61

PME_STS5 and PME_EN5 for GP50-GP57

The following GPIOs can directly generate an SMI and have a status and enable bit in the SMI status and enable

registers.

ꢀ

ꢀ

ꢀ

ꢀ

ꢀ

GP20-GP22, GP24-GP26

GP30-GP33

GP41, GP42, GP43

GP54-GP57

GP60, GP61

The following SMI status and enable registers for these GPIOs:

ꢀ

ꢀ

ꢀ

SMI_STS3 and SMI_EN3 for GP20-GP22, GP24-GP26 and GP60

SMI_STS4 and SMI_EN4 for GP30-GP33, GP41, GP42, GP43 and GP61

SMI_STS5 and SMI_EN5 for GP54-GP57, FAN_TACH1 and FAN_TACH2

SMSC DS – LPC47M14X

Page 113

Rev. 03/19/2001

SMSC [ SMSC CORPORATION ]

SMSC [ SMSC CORPORATION ]