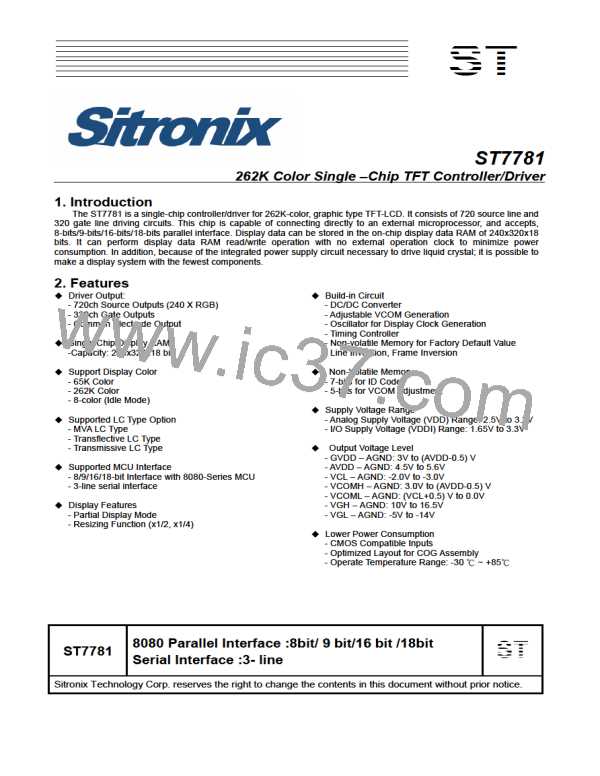

ST7781

DRAM Address map table of SS=1, BGR=1

SS = ’0’

S1 S2 S3

S4 S5 S6

------

-------

-------

S715 S716 S717 S718 S719 S720

S4 S5 S6 S1 S2 S3

SS = ’1’ S718 S719 S720 S715 S716 S717

BGR=’0’

BGR=’1’

R

B

G

B

R

R

B

G

B

R

R

B

G

B

R

R

B

G

B

R

G

G

G

G

X Address

Y Address

X Address

Y Address

“0000”h

“0000”h

“0000”h

“0001”h

“0001”h

“0000”h

“0001”h

“0001”h

“00EE”h

“0000”h

“00EE”h

“0001”h

“00EF”h

“0000”h

“00EF”h

“0001”h

-------

-------

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-------

X Address

Y Address

X Address

Y Address

“0000”h

“013E”h

“0000”h

“013F”h

“0001”h

“013E”h

“0001”h

“013F”h

“00EE”h

“013E”h

“00EE”h

“013F”h

“00EF”h

“013E”h

“00EF”h

“013F”h

-------

-------

Fig.9.12 DRAM Address Map Table

Note:

X Address Start Instruction

:

R50h

X Address End Instruction

:

R51h

Y Address Start Instruction

:

R52h

Y Address End Instruction

:

R53h

SS/GS Setting Instruction

:

R01h

BGR Setting Instruction:R03h

Ver. 1.7

39

SITRONIX [ SITRONIX TECHNOLOGY CO., LTD. ]

SITRONIX [ SITRONIX TECHNOLOGY CO., LTD. ]