ST7735

9.4 Data Transfer Break and Recovery

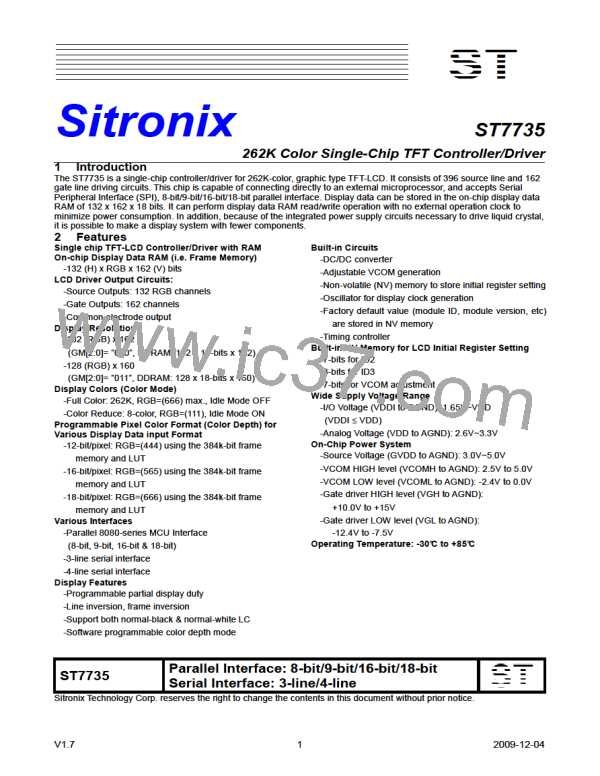

If there is a break in data transmission by RESX pulse, while transferring a command or frame memory data or multiple

parameter command data, before Bit D0 of the byte has been completed, then driver will reject the previous bits and have

reset the interface such that it will be ready to receive command data again when the chip select line (CSX) is next

activated after RESX have been HIGH state. See the following example

Fig. 9.4.1 Serial bus protocol, write mode – interrupted by RESX

If there is a break in data transmission by CSX pulse, while transferring a command or frame memory data or multiple

parameter command data, before Bit D0 of the byte has been completed, then driver will reject the previous bits and have

reset the interface such that it will be ready to receive the same byte re-transmitted when the chip select line (CSX) is next

activated. See the following example

Fig. 9.4.2 Serial bus protocol, write mode – interrupted by CSX

If 1, 2 or more parameter commands are being sent and a break occurs while sending any parameter before the last one

and if the host then sends a new command rather than re-transmitting the parameter that was interrupted, then the

parameters that were successfully sent are stored and the parameter where the break occurred is rejected. The interface is

ready to receive next byte as shown below.

V1.7

33

2009-12-04

SITRONIX [ SITRONIX TECHNOLOGY CO., LTD. ]

SITRONIX [ SITRONIX TECHNOLOGY CO., LTD. ]