SX1232

WIRELESS & SENSING

DATASHEET

3.4. Transmitter Description

The transmitter of SX1232 comprises the frequency synthesizer, modulator and power amplifier blocks, together with the

DC biasing and ramping functionality that is provided through the VR_PA block.

3.4.1. Architecture Description

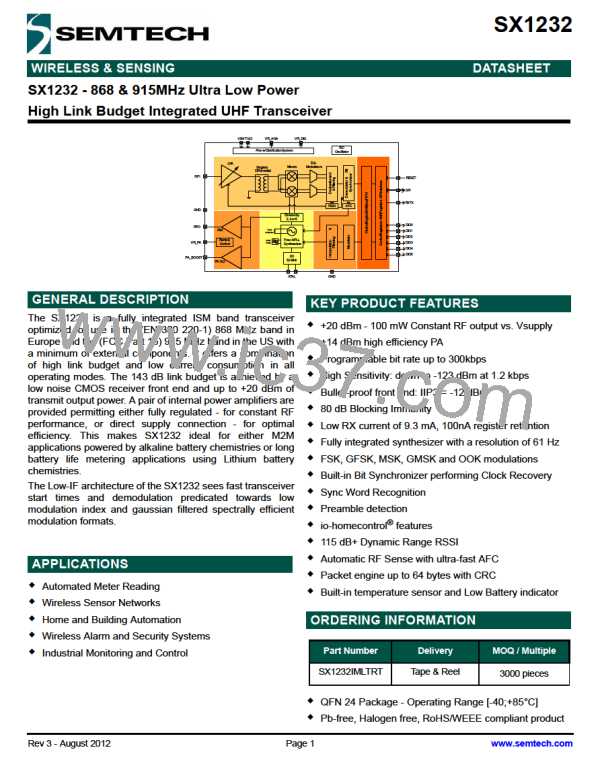

The architecture of the RF front end is shown in the following diagram. Here we see that the unregulated PA0 is connected

to the RFO pin features a single low power amplifier device. The PA_BOOST pin is connected to the internally regulated

PA1 and PA2 circuits. Here PA2 is a high power amplifier that permits continuous operation up to +17 dBm and duty cycled

operation up to +20 dBm. For full details of operation at +20 dBm please consult Section 3.4.7.

LNA

ReceiverChain

RFI

PA 0

RFO

Local

Oscillator

PA 1

PA 2

PA _BOOST

Figure 7. RF Front-end Architecture Shows the Internal PA Configuration.

3.4.2. Bit Rate Setting

The bitrate setting is referenced to the crystal oscillator and provides a precise means of setting the bit (or equivalently

chip) rate of the radio. In continuous transmit mode (Section 3.2.2) the data stream to be transmitted can be input directly

to the modulator via pin 9 (DIO2/DATA) in an asynchronous manner, unless Gaussian filtering is used, in which case the

DCLK signal on pin 10 (DIO1/DCLK) is used to synchronize the data stream. See section 3.4.5 for details on the Gaussian

filter.

In Packet mode or in Continuous mode with Gaussian filtering enabled, the Bit Rate (BR) is controlled by bits Bitrate in

RegBitrateMsb and RegBitrateLsb

FXOSC

------------------------------------------------------------------------

BitRate =

BitrateFrac

-------------------------------

BitRate(15,0) +

16

Note BitrateFrac bits have no effect (i.e may be considered equal to 0) in OOK modulation mode

The quantity BitrateFrac is hence designed to allow very high precision (max. 250 ppm calculation error) for any bitrate in

the programmable range. Table 9 below shows a range of standard bitrates and the accuracy to within which they may be

reached.

Rev 3 - August 2012

Page 22

www.semtech.com

SEMTECH [ SEMTECH CORPORATION ]

SEMTECH [ SEMTECH CORPORATION ]