DDR SDRAM 512Mb C-die (x4, x8, x16)

DDR SDRAM

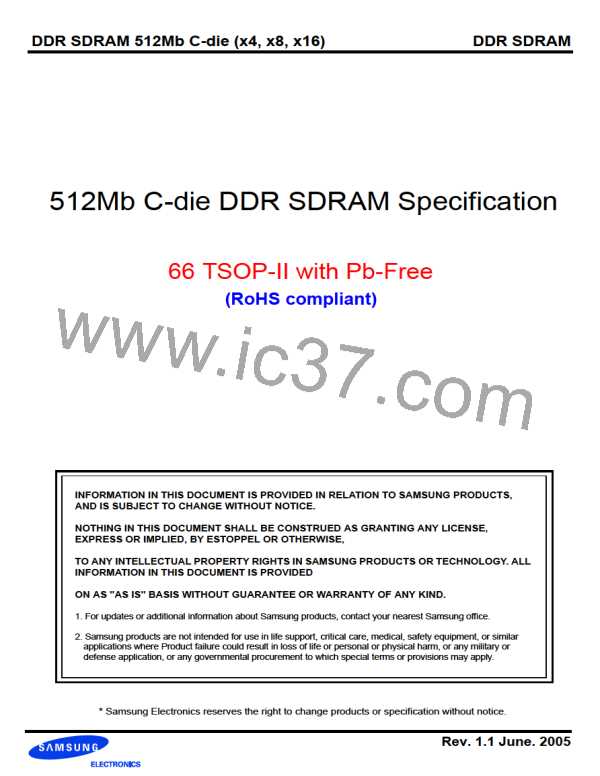

4.0 Pin Description

32Mb x 16

64Mb x 8

128Mb x 4

V

SS

V

SS

V

SS

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

1

V

DD

V

DD

V

DD

NC

DQ

7

DQ15

2

DQ

0

DQ

0

NC

DDQ

NC

VSSQ

VSSQ

VSSQ

3

VDDQ

VDDQ

V

NC

DQ

NC

DQ

DQ14

DQ13

4

DQ

1

2

NC

3

6

5

DQ

DQ

1

DQ

0

VDDQ

VDDQ

VDDQ

6

VSSQ

VSSQ

VSSQ

NC

NC

NC

DQ

DQ12

DQ11

7

DQ

3

4

NC

NC

NC

DDQ

NC

5

8

DQ

DQ

2

DDQ

NC

VSSQ

VSSQ

VSSQ

9

VDDQ

V

V

NC

DQ

NC

DQ

DQ10

10

11

12

13

14

15

16

17

18

19

20

21

22

23

DQ

5

6

66Pin TSOPII

(400mil x 875mil)

(0.65mm Pin Pitch)

2

4

DQ

9

DQ

DQ

3

DQ

1

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

NC

NC

NC

NC

DQ

8

DQ

7

NC

NC

DDQ

NC

NC

NC

NC

DDQ

NC

NC

NC

NC

Bank Address

BA0~BA1

VSSQ

VSSQ

VSSQ

VDDQ

V

V

DQS

NC

DQS

NC

UDQS

NC

LDQS

NC

Auto Precharge

A10

VREF

VREF

VREF

VDD

VDD

VDD

VSS

VSS

VSS

NC

LDM

WE

NC

NC

NC

NC

DM

CK

DM

CK

UDM

CK

WE

CAS

RAS

CS

WE

CAS

RAS

CS

CK

CK

CK

CAS

RAS

CS

CKE

NC

CKE

NC

CKE

NC

24

25

26

27

28

29

30

31

32

33

A

A

A

A

A

A

A

A

12

11

9

A

A

A

A

A

A

A

A

12

11

9

A

A

A

A

A

A

A

A

12

11

9

NC

NC

NC

BA

0

BA

0

BA

0

BA

1

BA

1

BA

1

8

8

8

AP/A10

AP/A10 AP/A10

7

7

7

A

A

A

A

0

1

2

3

A

A

A

A

0

1

2

3

A

A

A

A

0

1

2

3

6

6

6

5

5

5

4

4

4

VSS

VSS

VSS

VDD

VDD

VDD

512Mb TSOP-II Package Pinout

Organization

128Mx4

Row Address

A0~A12

Column Address

A0-A9, A11, A12

A0-A9, A11

64Mx8

A0~A12

32Mx16

A0~A12

A0-A9

DM is internally loaded to match DQ and DQS identically.

Row & Column address configuration

Rev. 1.1 June. 2005

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]