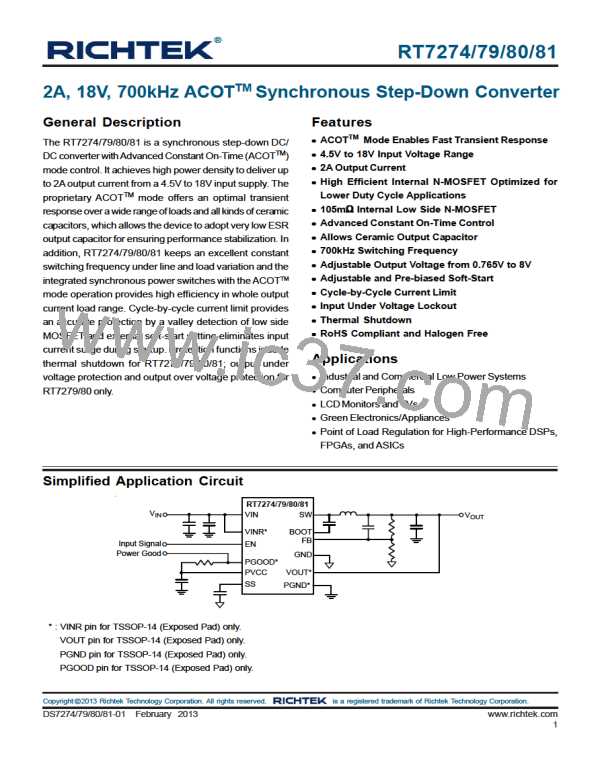

RT7274/79/80/81

package, the thermal resistance, θJA, is 49°C/W on a

standard JEDEC 51-7 four-layer thermal test board. The

maximum power dissipation at TA= 25°C can be calculated

by the following formulas :

Layout Consideration

Follow the PCB layout guidelines for optimal performance

of the RT7274/79/80/81

` Keep the traces of the main current paths as short and

PD(MAX) = (125°C − 25°C) / (40°C/W) = 2.50W for

wide as possible.

TSSOP-14 (Exposed Pad) package

` Put the input capacitor as close as possible to the device

PD(MAX) = (125°C − 25°C) / (49°C/W) = 2.04W for

pins (VINandGND).

SOP-8 (Exposed Pad) package

` SW node is with high frequency voltage swing and

should be kept at small area. Keep sensitive

components away from the SW node to prevent stray

capacitive noise pickup.

The maximum power dissipation depends on operating

ambient temperature for fixed TJ(MAX) and thermal

resistance, θJA. The derating curves in Figure 6 allow the

designer to see the effect of rising ambient temperature

on the maximum power dissipation.

` Connect feedback network behind the output capacitors.

Keep the loop area small. Place the feedback

components near the RT7274/79/80/81 FB pin.

3.0

Four-Layer PCB

TSSOP-14 (Exposed Pad)

` The GND and Exposed Pad should be connected to a

2.5

2.0

strong ground plane for heat sinking and noise protection.

Place the input and output

capacitors as close to the

IC as possible.

Place the feedback components

as close to the FB as possible

for better regulation.

1.5

SOP-8 (Exposed Pad)

V

OUT

PGND

1.0

0.5

0.0

R1

C

IN

14

13

VINR

VIN

BOOT

SW

SW

PGND

PGND

VOUT

2

3

4

5

6

7

FB

PVCC

SS

GND

PGOOD

EN

C

BOOT

12

11

10

9

R2

C

VCC

PGND

L

V

OUT

0

25

50

75

100

125

15

8

Ambient Temperature (°C)

C

OUT

Figure 6.Derating Curve of Maximum PowerDissipation

SW should be connected to inductor by

Wide and short trace. Keep sensitive

components away from this trace.

(a). For TSSOP-14 (Exposed Pad) Package

The resistor divider must

be connected as close to

the device as possible.

Input capacitor must be placed

as close to the IC as possible.

C1

C2

V

OUT

SW should be connected to inductor by

Wide and short trace. Keep sensitive

components away from this trace.

R1

8

7

6

5

EN

FB

VIN

R2

C4

C5

2

3

4

BOOT

SW

GND

C6

GND

PVCC

SS

9

L1

GND

C7

(b). For SOP-8 (Exposed) Package

Figure 7. PCB Layout Guide

Copyright 2013 Richtek Technology Corporation. All rights reserved.

©

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

20

DS7274/79/80/81-01 February 2013

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]