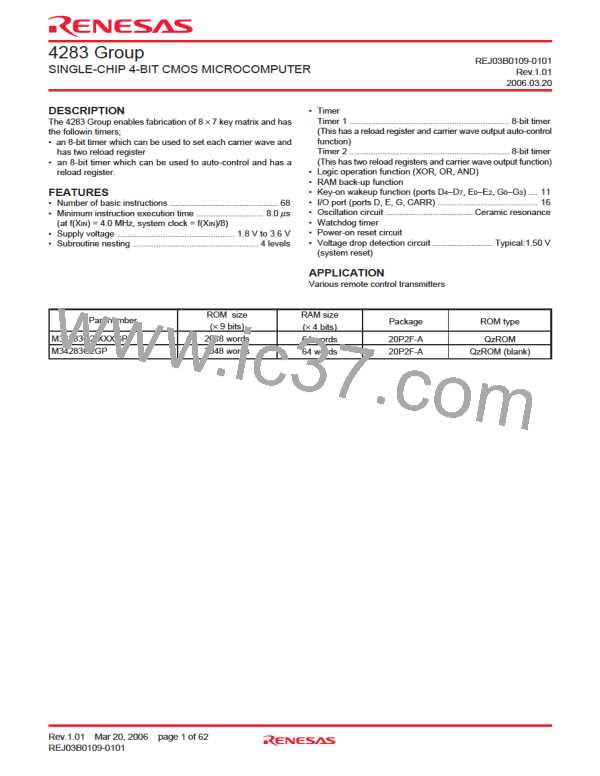

4283 Group

REGISTER STRUCTURE

Timer control register V1

at reset : 0002

at RAM back-up : 0002

W

0

1

0

1

0

1

Auto-control output by timer 1 is invalid

Auto-control output by timer 1 is valid

Carrier wave output (CARRY)

Bit 5 of watchdog timer (WDT)

Stop (Timer 1 state retained)

Operating

V12

V11

V10

Carrier wave output auto-control bit

Timer 1 count source selection bit

Timer 1 control bit

Timer control register V2

at reset : 00002

at RAM back-up : 00002

W

0

1

0

1

0

1

0

1

To expand “H” interval is invalid

To expand “H” interval is valid (when V22=1 selected)

Carrier wave generation function invalid

Carrier wave generation function valid

f(XIN)

V23

V22

V21

V20

Carrier wave “H” interval expansion bit

Carrier wave generation function control bit

Timer 2 count source selection bit

Timer 2 control bit

f(XIN)/2

Stop (Timer 2 state retained)

Operating

Logic operation selection register LO

Logic operation selection bits

at reset : 002

LO1 LO0

W

at RAM back-up : 002

Logic operation function

0

0

1

1

0

1

0

1

Exclusive logic OR operation (XOR)

LO1

LO0

OR operation (OR)

AND operation (AND)

Not available

Pull-down control register PU0

at reset : 00002

at RAM back-up : state retained

W

Ports G2, G3 pull-down transistor control

Pull-down transistor OFF, key-on wakeup invalid

Pull-down transistor ON, key-on wakeup valid

Pull-down transistor OFF, key-on wakeup invalid

Pull-down transistor ON, key-on wakeup valid

Pull-down transistor OFF, key-on wakeup invalid

Pull-down transistor ON, key-on wakeup valid

Pull-down transistor OFF, key-on wakeup invalid

Pull-down transistor ON, key-on wakeup valid

0

1

0

1

0

1

0

1

PU03

PU02

PU01

PU00

bit

Ports G0, G1 pull-down transistor control

bit

Port E1 pull-down transistor control bit

Port E0 pull-down transistor control bit

Pull-down control register PU1

at reset : 00002

at RAM back-up : state retained

W

Pull-down transistor OFF, key-on wakeup invalid

Pull-down transistor ON, key-on wakeup valid

Pull-down transistor OFF, key-on wakeup invalid

Pull-down transistor ON, key-on wakeup valid

Pull-down transistor OFF, key-on wakeup invalid

Pull-down transistor ON, key-on wakeup valid

Pull-down transistor OFF, key-on wakeup invalid

Pull-down transistor ON, key-on wakeup valid

0

1

0

1

0

1

0

1

PU13

PU12

PU11

PU10

Port D7 pull-down transistor control bit

Port D6 pull-down transistor control bit

Port D5 pull-down transistor control bit

Port D4 pull-down transistor control bit

Rev.1.01 Mar 20, 2006 page 59 of 62

REJ03B0109-0101

RENESAS [ RENESAS TECHNOLOGY CORP ]

RENESAS [ RENESAS TECHNOLOGY CORP ]