TransDimension

TD243

Product Brief

ꢀ LEimnubxe,dVdxeWd oRrTksO,SNsuocfletwuasr,eLyanvxaOilaSb,leQfNoXr W, piSnCOES,,

ꢀ Programmable DMA and IRQ polarities

ꢀ 1av0a0ilpaibnleLQFP and 84 ball TF-BGA packages

PowerTV, SMX, AMX, ThreadX, VRTX, ITRON,

Symbian OS and MS-DOS operating systems

among others

ꢀ UprSinBtedr,esvpiceeadkreivr,emr saosfstwsatoreraagvea, ihlaubble, minocdluedmin,g

Ethernet, mouse, keyboard, digital camera, video

camera, cell phone, STB, PDA, etc.

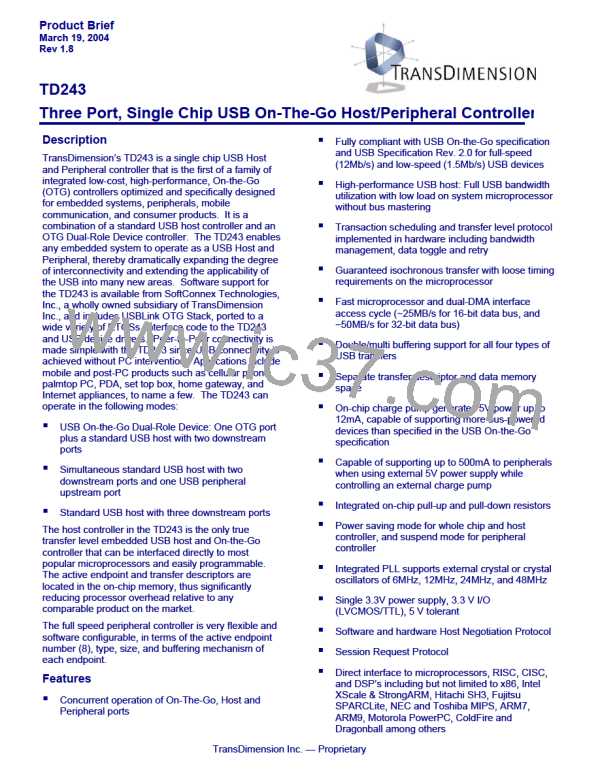

Architecture

OSC1

OSC2

CEX1

48 MHz

12 MHz

+5V (VBus)

PLL

CEX2

Charge Pump

VFB

&

PSC

VBUS

VBus Control

System

VBP

Configuration

&

/RESET

Control

Registers

/CS

/WR

/RD

HNP/ SRP

Logic

PSH

PSF

ID

USB Peripheral

Controller

DRQ1

DACK1

EOT1

USB

Peripheral

Control

Logic

H/F

Peripheral

Registers

µP

Interface

SIE

RPU

DRQ0

OTG

DACK0

EOT0

Trans-

ceiver

DM1

DP1

PSH

Memory

Blocks

USB

Trans-

ceiver

A8:A2

DM2

DP2

Host

SIE

&

D31:D0

USB

Host

INT

WAKEUP

/EXVBO

USB

Trans-

ceiver

Root

Hub

DM3

DP3

Control

Logic

USB Host

Controller

Registers

Test

Controller

TEST

/PO

/OC

Figure 1 – TD243 Architectural Block Diagram

USB/OTG Host logic blocks: The USB Host Controller Logic, the host Serial Interface Engine (SIE) and the root

hub are responsible for the fully complaint (not reduced) USB host of the TD243 - supporting transfer level user

interface, scheduling/processing transactions, and monitoring/handling port events.

USB/OTG Peripheral logic blocks: The USB Peripheral Controller Logic, together with the peripheral SIE,

manages all low-level USB peripheral protocols upon which a fully compliant full speed USB peripheral is operated.

Direct Memory Access: Two DMA channels allow fast data movement between the application and the TD243

with minimum intervention from the microprocessor. Programmed accesses to the TD243 through DMA and those

through memory mapped, programmed I/Os can be interleaved.

Interrupt Handling: Interrupts from the TD243 to a microprocessor are minimum, as an interrupt is generated only

at the end of a USB transfer (for both host and peripheral), which can have a size of up to 4 Mbytes*. Moreover, an

2

TransDimension Inc. — Proprietary

OXFORD [ OXFORD SEMICONDUCTOR ]

OXFORD [ OXFORD SEMICONDUCTOR ]