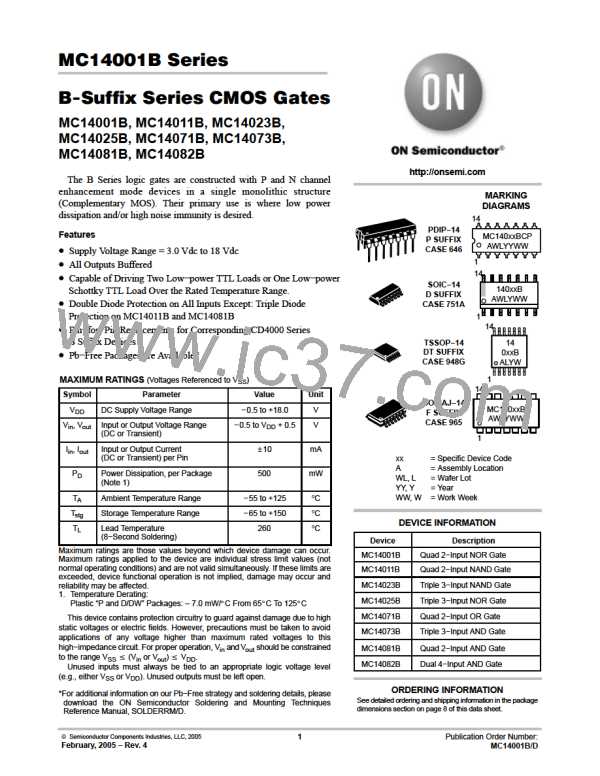

MC14001B Series

B−SERIES GATE SWITCHING TIMES

SWITCHING CHARACTERISTICS (5) (C = 50 pF, T = 25_C)

L

A

V

DD

Vdc

(6)

Characteristic

Symbol

Min

Typ

Max

Unit

Output Rise Time, All B−Series Gates

t

ns

TLH

t

t

t

= (1.35 ns/pF) C + 33 ns

L

TLH

TLH

TLH

5.0

10

15

−

−

−

100

50

40

200

100

80

= (0.60 ns/pF) C + 20 ns

L

= (0.40 ns/PF) C + 20 ns

L

Output Fall Time, All B−Series Gates

t

ns

ns

THL

t

t

t

= (1.35 ns/pF) C + 33 ns

L

THL

THL

THL

5.0

10

15

−

−

−

100

50

40

200

100

80

= (0.60 ns/pF) C + 20 ns

L

= (0.40 ns/pF) C + 20 ns

L

Propagation Delay Time

t

, t

PLH PHL

MC14001B, MC14011B only

t

t

t

, t

= (0.90 ns/pF) C + 80 ns

= (0.36 ns/pF) C + 32 ns

L

5.0

10

15

−

−

−

125

50

40

250

100

80

PLH PHL

L

, t

PLH PHL

, t

= (0.26 ns/pF) C + 27 ns

PLH PHL

L

All Other 2, 3, and 4 Input Gates

t

t

t

, t

= (0.90 ns/pF) C + 115 ns

= (0.36 ns/pF) C + 47 ns

L

5.0

10

15

−

−

−

160

65

50

300

130

100

PLH PHL

L

, t

PLH PHL

, t

= (0.26 ns/pF) C + 37 ns

PLH PHL

L

8−Input Gates (MC14068B, MC14078B)

t

t

t

, t

= (0.90 ns/pF) C + 155 ns

= (0.36 ns/pF) C + 62 ns

L

5.0

10

15

−

−

−

200

80

60

350

150

110

PLH PHL

L

, t

PLH PHL

, t

= (0.26 ns/pF) C + 47 ns

PLH PHL

L

5. The formulas given are for the typical characteristics only at 25_C.

6. Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

20 ns

20 ns

14

V

DD

V

DD

90%

50%

10%

INPUT

INPUT

*

0 V

PULSE

OUTPUT

t

t

PLH

GENERATOR

PHL

90%

50%

10%

V

V

OH

C

L

OUTPUT

OL

INVERTING

t

t

TLH

THL

t

t

PHL

PLH

V

V

OH

7

V

SS

OUTPUT

90%

50%

10%

NON−INVERTING

*All unused inputs of AND, NAND gates must be connected to V

.

OL

DD

t

t

THL

TLH

All unused inputs of OR, NOR gates must be connected to V

.

SS

Figure 1. Switching Time Test Circuit and Waveforms

http://onsemi.com

4

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]