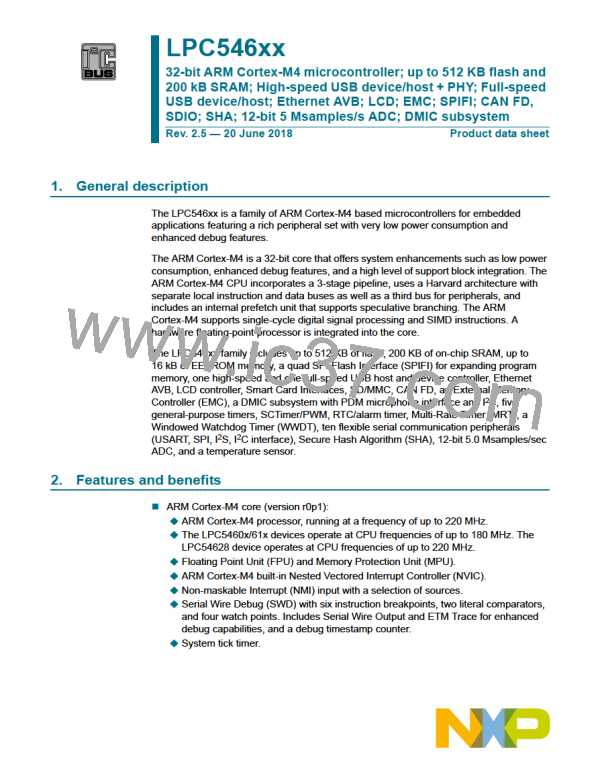

LPC546xx

NXP Semiconductors

32-bit ARM Cortex-M4 microcontroller

JTAG test and

FS USB

bus or

ISP access boundary scan

ethernet

PHY interface

LCD

panel

SDIO

CAN

interface

port

interface

transceiver interface

Xtalin Xtalout RST

CLOCK GENERATION,

DEBUG INTERFACE

GENERAL

PURPOSE

DMA

ETHERNET

10/100

MAC

USB 2.0

LCD

clocks

and

controls

POWER CONTROL,

AND OTHER

CAN

FD

CAN

FD

SHA

CLK

OUT

HOST/

SDIO

PANEL

ARM CORTEX-M4

WITH FPU/MPU

DEVICE

INTERFACE

SYSTEM FUNCTIONS

CONTROLLER

+AVB

H

D

internal

power

I-code D-code system

Vdd

VOLTAGE REGULATOR

bus

bus

bus

BOOT ROM

64 kB

HS USB

PHY

HS USB

bus

FLASH

INTERFACE

AND

FLASH

512 MB

ACCELERATOR

SRAM

32 kB

SPI FLASH

INTERFACE

SPIFI

SRAM

64 kB

SRAM

32 kB

MULTILAYER

AHB MATRIX

SRAM

32 kB

SRAM

32 kB

FS USB

HOST

REGISTERS

HS USB

HOST

REGISTERS

12b ADC

12-CH

ADC

inputs

SHA SLAVE

INTERFACE

POLYFUSE OTP

256 b

TEMP

SENSOR

EEPROM

UP TO 16 kB

USB RAM

INTERFACE

SRAM

8 kB

D[31:0]

A[25:0]

control

GPIO

STATIC/DYNAMIC EXT

MEMORY CONTROLLER

HS GPIO

0-5

SPIFI

REGISTERS

EMC

REGISTERS

DMA

REGISTERS

LCD

REGISTERS

FS USB

DEVICE

REGISTERS

SCTimer/

PWM

FlexComms 0-4

-UARTs 0-4 - I2Cs 0-4

-SPI0s 0-4

CAN 0

CAN 1

ETHERNET

REGISTERS

HS USB

DEVICE

CRC

SDIO

FlexComms 5-9

REGISTERS

REGISTERS

ENGINE

REGISTERS

-UARTs 5-9

REGISTERS

-SPI0s 5-9

-I2Cs 5-9 - I2Ss 0,1

AUDIO SUBSYS

D-MIC,

DECIMATOR, ETC

AHB TO

APB BRIDGE

APB slave group 0

ASYNC AHB TO

APB BRIDGE

APB slave group 2

SYSTEM CONTROL

SYSTEM CONTROL (async regs)

I/O CONFIGURATION

AHB TO

APB BRIDGE

2 x 32-BIT TIMERS (T3, 4)

GPIO GLOBAL INTRPTS (0, 1)

GPIO INTERRUPT CONTROL

PERIPH INPUT MUX SELECTS

2 x 32-BIT TIMERS (T0, 1)

MULTI-RATE TIMER

APB slave group 1

PMU REGS (+BB, PVT)

32-BIT TIMERS (T2)

RIT

FLASH 0 REGISTERS

2 x SMARTCARDS

RANDOM NUMBER GEN

EEPROM REGISTERS

OTP CONTROLLER

RTC POWER

RTC ALARM

WATCHDOG

OSC

WINDOWED WDT

DOMAIN

REAL TIME

CLOCK

32 kHz

Osc

DIVIDER

MICRO TICK TIMER

Note:

- Orange shaded blocks support Gen. Purpose DMA.

- Yellow shaded blocks include dedicated DMA Ctrl.

aaa-029364

Fig 4. LPC546xx Block diagram

LPC546xx

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

Product data sheet

Rev. 2.5 — 20 June 2018

10 of 169

NXP [ NXP ]

NXP [ NXP ]