Numonyx™ Wireless Flash Memory (W18)

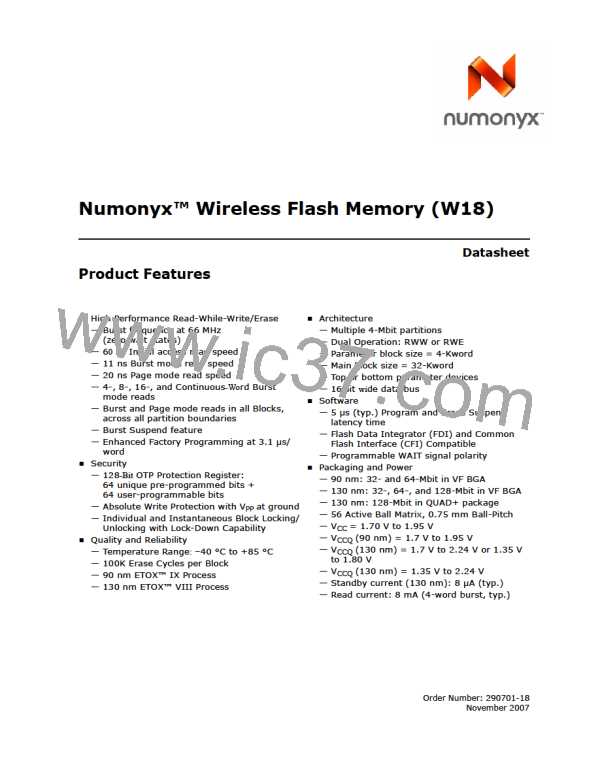

Table 23: Bus Cycle Definitions

First Bus Cycle

Addr1

Second Bus Cycle

Bus

Cycles

Operation

Command

Oper

Data2,3

Oper

Addr1

Data2,3

Protection Program

2

2

2

Write

PA

LPA

CD

C0h

Write

Write

Write

PA

PD

FFFDh

03h

Protection

Lock Protection Program

Set Configuration Register

Write

Write

C0h

60h

LPA

CD

Configuration

Notes:

1.

First-cycle command addresses should be the same as the operation’s target address. Examples: the first-cycle address

for the Read Identifier command should be the same as the Identification code address (IA); the first-cycle address for

the Word Program command should be the same as the word address (WA) to be programmed; the first-cycle address

for the Erase/Program Suspend command should be the same as the address within the block to be suspended; etc.

XX = Any valid address within the device.

IA = Identification code address.

BA = Block Address. Any address within a specific block.

LPA = Lock Protection Address is obtained from the CFI (through the CFI Query command). The Numonyx Wireless

Flash Memory (W18) family’s LPA is at 0080h.

PA = User programmable 4-word protection address.

PnA = Any address within a specific partition.

PBA = Partition Base Address. The very first address of a particular partition.

QA = CFI code address.

WA = Word address of memory location to be written.

SRD = Status register data.

WD = Data to be written at location WA.

2.

IC = Identifier code data.

PD = User programmable 4-word protection data.

QD = Query code data on DQ[7:0].

CD = Configuration register code data presented on device addresses A[15:0]. A[MAX:16] address bits can select any

partition. See Table 31, “Read Configuration Register Descriptions” on page 78 for Configuration

Register bits descriptions.

Commands other than those shown above are reserved by Numonyx for future device implementations and should not

be used.

3.

9.3

Command Sequencing

When issuing a 2-cycle write sequence to the flash device, a read operation is allowed

to occur between the two write cycles. The setup phase of a 2-cycle write sequence

places the addressed partition into read-status mode, so if the same partition is read

before the second “confirm” write cycle is issued, Status Register data will be returned.

Reads from other partitions, however, can return actual array data assuming the

addressed partition is already in read-array mode. Figure 23 and Figure 24 illustrate

these two conditions.

November 2007

Order Number: 290701-18

Datasheet

53

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]