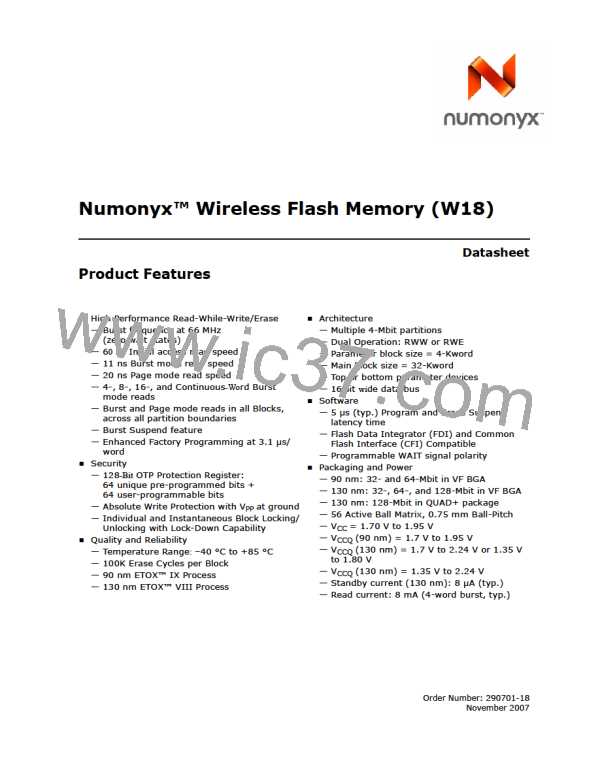

Numonyx™ Wireless Flash Memory (W18)

Table 8:

Signal Descriptions - QUAD+ Package (Sheet 1 of 2)

Symbol

Type

Description

ADDRESS INPUTS: Inputs for all die addresses during read and write operations.

—256-Mbit Die : AMAX= A23

—128-Mbit Die : AMAX = A22

—64-Mbit Die : AMAX = A21

—32-Mbit Die : AMAX = A20

A[MAX:MIN]

Input

—8-Mbit Die : AMAX = A18

A0 is the lowest-order 16-bit wide address.

A[25:24] denote high-order addresses reserved for future device densities.

DATA INPUTS/OUTPUTS: Inputs data and commands during write cycles, outputs data during read

cycles. Data signals float when the device or its outputs are deselected. Data are internally latched

during writes on the flash device.

Input/

Output

D[15:0]

FLASH CHIP ENABLE: Low-true input.

F[3:1]-CE# low selects the associated flash memory die. When asserted, flash internal control logic,

input buffers, decoders, and sense amplifiers are active. When deasserted, the associated flash die is

deselected, power is reduced to standby levels, data and WAIT outputs are placed in high-Z state.

F1-CE# selects or deselects flash die #1; F2-CE# selects or deselects flash die #2 and is RFU on

combinations with only one flash die. F3-CE# selects or deselects flash die #3 and is RFU on stacked

combinations with only one or two flash dies.

F[3:1]-CE#

Input

Input

Input

SRAM CHIP SELECT: Low-true / High-true input (S-CS1# / S-CS2 respectively).

When either/both SRAM Chip Select signals are asserted, SRAM internal control logic, input buffers,

decoders, and sense amplifiers are active. When either/both SRAM Chip Select signals are deasserted,

the SRAM is deselected and its power is reduced to standby levels.

S-CS1# and S-CS2 are available on stacked combinations with SRAM die and are RFU on stacked

combinations without SRAM die.

S-CS1#

S-CS2

PSRAM CHIP SELECT: Low-true input.

When asserted, PSRAM internal control logic, input buffers, decoders, and sense amplifiers are active.

When deasserted, the PSRAM is deselected and its power is reduced to standby levels.

P1-CS# selects PSRAM die #1 and is available only on stacked combinations with PSRAM die. This ball

is an RFU on stacked combinations without PSRAM. P2-CS# selects PSRAM die #2 and is available only

on stacked combinations with two PSRAM dies. This ball is an RFU on stacked combinations without

PSRAM or with a single PSRAM.

P[2:1]-CS#

FLASH OUTPUT ENABLE: Low-true input.

Fx-OE# low enables the selected flash’s output buffers. F[2:1]-OE# high disables the selected flash’s

output buffers, placing them in High-Z.

F1-OE# controls the outputs of flash die #1; F2-OE# controls the outputs of flash die #2 and flash die

#3. F2-OE# is available on stacked combinations with two or three flash die and is RFU on stacked

combinations with only one flash die.

F[2:1]-OE#

R-OE#

Input

Input

RAM OUTPUT ENABLE: Low-true input.

R-OE# low enables the selected RAM’s output buffers. R-OE# high disables the RAM output buffers,

and places the selected RAM outputs in High-Z.

R-OE# is available on stacked combinations with PSRAM or SRAM die, and is an RFU on flash-only

stacked combinations.

FLASH WRITE ENABLE: Low-true input.

F-WE#

R-WE#

Input

Input

F-WE# controls writes to the selected flash die. Address and data are latched on the rising edge of F-

WE#.

RAM WRITE ENABLE: Low-true input.

R-WE# controls writes to the selected RAM die.

R-WE# is available on stacked combinations with PSRAM or SRAM die and is an RFU on flash-only

stacked combinations.

CLOCK: Synchronizes the flash die with the system bus clock in synchronous read mode and

increments the internal address generator.

During synchronous read operations, addresses are latched on the rising edge of ADV#, or on the next

valid CLK edge with ADV# low, whichever occurs first.

CLK

Input

In asynchronous mode, addresses are latched on the rising edge ADV#, or are continuously flow-

through when ADV# is kept asserted.

November 2007

Order Number: 290701-18

Datasheet

19

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]