DDR3(L) 4Gb SDRAM

NT5CB(C)512M8DN / NT5CB(C)256M16DP

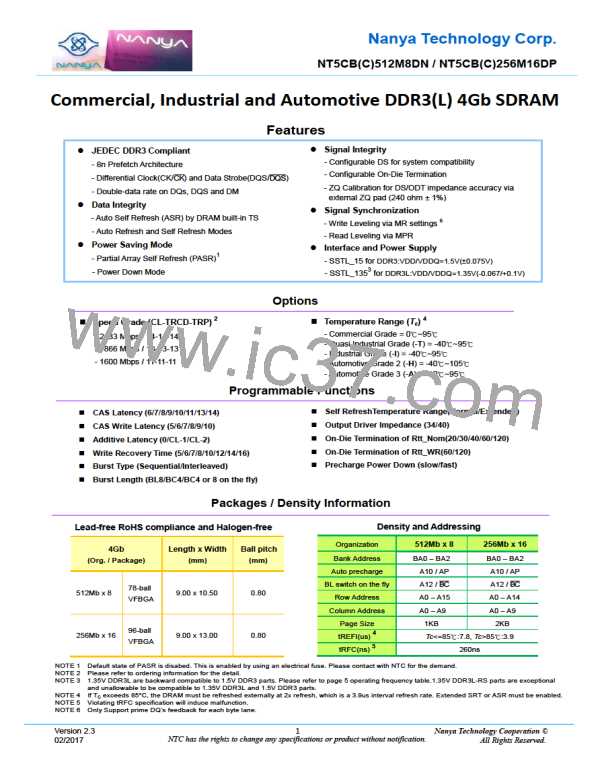

DLL-off mode READ Timing Operation

T0

T1

T2

T3

T4

T5

T6

T7

T8

T9

CK

CK

CMD

Address

READ

Bank, Col b

RL = AL+CL = 6 (CL=6, AL=0)

DQSdiff_DLL_on

DQ_DLL_on

Din

b

Din

b+1

Din

b+2

Din

b+3

Din

b+4

Din

b+5

Din

b+6

Din

b+7

RL(DLL_off) = AL+(CL-1) = 5

tDQSCKDLL_diff_min

DQSdiff_DLL_off

Din

b+4

Din

b

Din

b+1

Din

b+2

Din

b+3

Din

b+5

Din

b+6

Din

b+7

DQ_DLL_off

DQSdiff_DLL_off

tDQSCKDLL_diff_max

Din

b+4

Din

b

Din

b+1

Din

b+2

Din

b+3

Din

b+5

Din

b+6

Din

b+7

DQ_DLL_off

Note: The tDQSCK is used here for DQS, , and DQ to have a simplified diagram; the DLL_off shift will affect both timings in the same

way and the skew between all DQ, DQS, and signals will still be tDQSQ.

Version 2.3

02/2017

35

Nanya Technology Cooperation ©

All Rights Reserved.

NANYA [ Nanya Technology Corporation. ]

NANYA [ Nanya Technology Corporation. ]