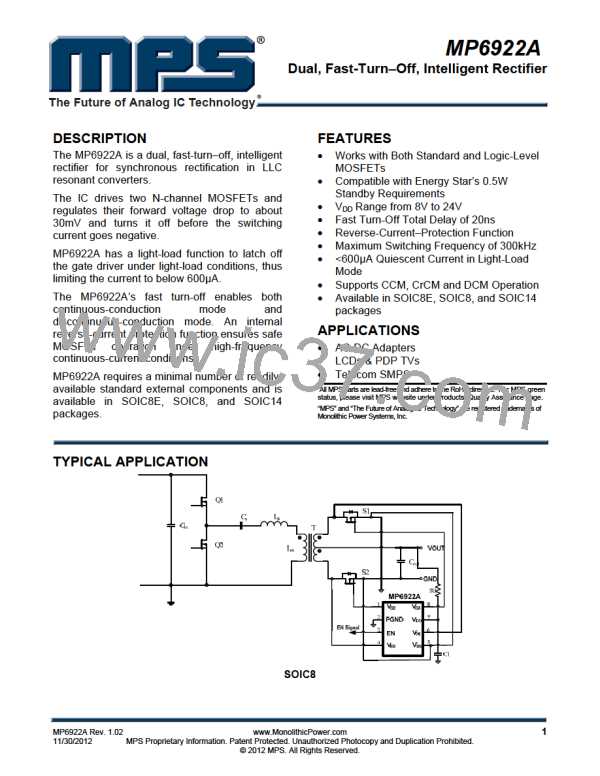

MP6922A—DUAL, FAST-TURN–OFF, INTELLIGENT RECTIFIER

Figure 4 shows the MP6922A operating at light-

After entering light-load mode, the MP6922A

monitors the MOSFET’s body diode conducting

period by sensing VDS (when VDS exceeds –

300mV (VLL-DS), MP6922A treats the the

MOSFET’s body-diode conducting period as

finished). If the MOSFET’s body diode

conducting period exceeds 2.4μs (τLL+τLL-H), light-

load mode ends and the MOSFET unlatches to

restart the synchronous rectification.

load. The low current prevents the driver voltage

from saturating but decreases when the

synchronous power switch turns on and adjusts

VDS.

Vds

0mV

-30mV

For the SOIC14 package. the MP6922A has an

LL pin that allows τLL to be adjusted by an

external resistor:

Isd

RLL

LL 2.2s

100k

Vgs

Latch Off during Burst Operation

The IC also monitors the synchronous MOSFET

OFF period. If the OFF period exceeds the light-

load–enter OFF period width (τLL-OFF), the

MP6922A enters light-load mode and latches off

the gate driver.

Figure 3: Synchronous Rectification

Operation at Heavy Load

Vds

0mV

-30mV

The gate driver is unlatched when the drain-

source voltage of the synchronous MOSFET VDS

drops below –30mV.

Reverse Current–Protection Function

When the LLC system operates in CCM at a very

high frequency, the synchronous current may

reverse before the IC turns off the gate driver,

which can lead to shoot-through (in center-

tapped outputs with full-wave rectification

topologies). The MP6922A has a protection

function to latch off the gate driver when the

current reverses before the driver signal is pulled

low.

Isd

Vgs

Figure 4: Synchronous Rectification

Operation at Light Load

Light-Load Latch-Off Function

The gate driver of MP6922A is latched to limit

driver losses under light-load condition to

improve light-load efficiency.

When the synchronous current reverses, the high

spike can be observed between the MOSFET’s

drain/source. The MP6922A monitors the voltage

through the RCP pin using a voltage divider.

Normal Operation Latch Off

When the MOSFET’s switching-cycle conducting

period falls below 2.2μs (τLL), the MP6922A

enters light-load mode and latches off the

MOSFET after a 160μs delay (light-load-enter

When the voltage of RCP pin exceeds VRCP

MP6922A latches the driver signal of both

channels for ~150μs (τRCP) to protect the

synchronous MOSFET. At the end of τRCP

,

,

delay, τLL-Delay

)

MP6922A restarts the synchronous rectification.

MP6922A Rev. 1.02

11/30/2012

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2012 MPS. All Rights Reserved.

11

MPS [ MONOLITHIC POWER SYSTEMS ]

MPS [ MONOLITHIC POWER SYSTEMS ]