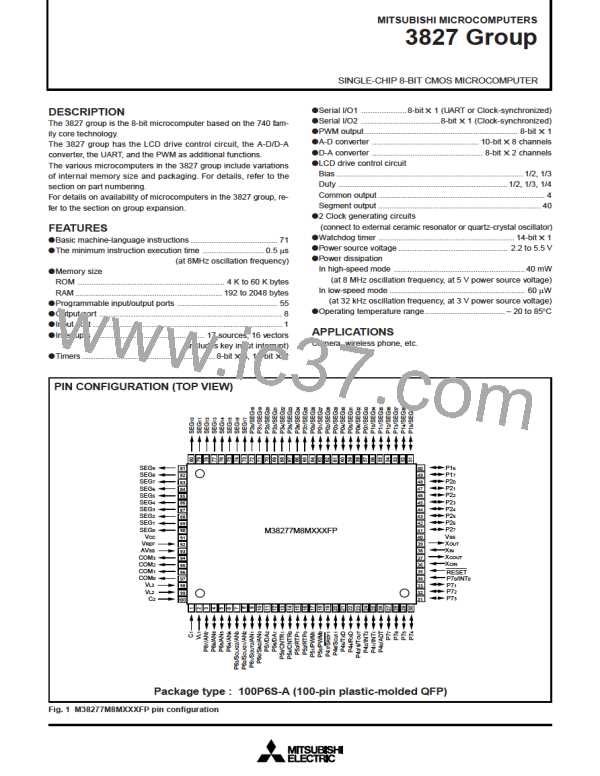

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

NOTES ON PROGRAMMING

Serial I/O

Processor Status Register

In clock synchronous serial I/O, if the receive side is using an ex-

ternal clock and it is to output the SRDY signal, set the transmit

enable bit, the receive enable bit, and the SRDY output enable bit

to “1”.

The contents of the processor status register (PS) after a reset are

undefined, except for the interrupt disable flag (I) which is “1”. Af-

ter a reset, initialize flags which affect program execution.

In particular, it is essential to initialize the index X mode (T) and

the decimal mode (D) flags because of their effect on calculations.

Serial I/O1 continues to output the final bit from the TXD pin after

transmission is completed.

In serial I/O2, the SOUT2 pin goes to high impedance state after

transmission is completed.

Interrupt

The contents of the interrupt request bits do not change immedi-

ately after they have been written. After writing to an interrupt

request register, execute at least one instruction before performing

a BBC or BBS instruction.

A-D Converter

The comparator uses internal capacitors whose charge will be lost

if the clock frequency is too low.

Make sure that f(XIN) is at least 500 kHz during an A-D conver-

Decimal Calculations

sion.

• To calculate in decimal notation, set the decimal mode flag (D)

to “1”, then execute an ADC or SBC instruction. After executing

an ADC or SBC instruction, execute at least one instruction be-

fore executing a SEC, CLC, or CLD instruction.

Do not execute the STP or WIT instruction during an A-D conver-

sion.

Instruction Execution Time

The instruction execution time is obtained by multiplying the fre-

quency of the internal clock φ by the number of cycles needed to

execute an instruction.

• In decimal mode, the values of the negative (N), overflow (V),

and zero (Z) flags are invalid.

The number of cycles required to execute an instruction is shown

in the list of machine instructions.

Timers

If a value n (between 0 and 255) is written to a timer latch, the fre-

The frequency of the internal clock φ is half of the XIN frequency.

quency division ratio is 1/(n + 1).

Multiplication and Division Instructions

The index mode (T) and the decimal mode (D) flags do not affect

the MUL and DIV instruction.

The execution of these instructions does not change the contents

of the processor status register.

Ports

The contents of the port direction registers cannot be read.

The following cannot be used:

• The data transfer instruction (LDA, etc.)

• The operation instruction when the index X mode flag (T) is “1”

• The addressing mode which uses the value of a direction regis-

ter as an index

• The bit-test instruction (BBC or BBS, etc.) to a direction register

• The read-modify-write instruction (ROR, CLB, or SEB, etc.) to a

direction register

Use instructions such as LDM and STA, etc., to set the port direc-

tion registers.

48

MITSUBISHI [ Mitsubishi Group ]

MITSUBISHI [ Mitsubishi Group ]