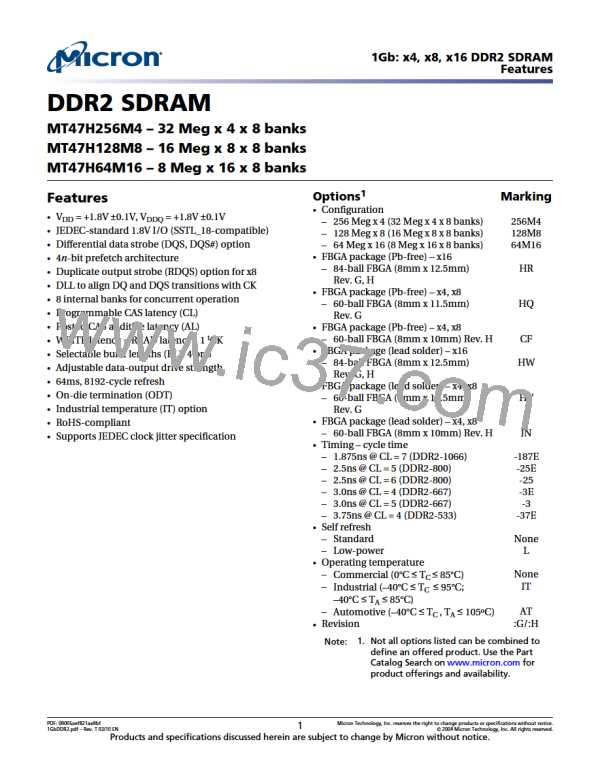

1Gb: x4, x8, x16 DDR2 SDRAM

Ball Assignments and Descriptions

Table 3: FBGA 84-Ball – x16 and 60-Ball – x4, x8 Descriptions (Continued)

Symbol

Type

Description

DQS, DQS#

I/O

Data strobe: Output with read data, input with write data for source synchronous oper-

ation. Edge-aligned with read data, center-aligned with write data. DQS# is only used

when differential data strobe mode is enabled via the LOAD MODE command.

LDQS, LDQS#

UDQS, UDQS#

RDQS, RDQS#

I/O

I/O

Data strobe for lower byte: Output with read data, input with write data for source

synchronous operation. Edge-aligned with read data, center-aligned with write data.

LDQS# is only used when differential data strobe mode is enabled via the LOAD MODE

command.

Data strobe for upper byte: Output with read data, input with write data for source

synchronous operation. Edge-aligned with read data, center-aligned with write data.

UDQS# is only used when differential data strobe mode is enabled via the LOAD MODE

command.

Output

Redundant data strobe: For x8 only. RDQS is enabled/disabled via the LOAD MODE com-

mand to the extended mode register (EMR). When RDQS is enabled, RDQS is output with

read data only and is ignored during write data. When RDQS is disabled, ball B3 becomes

data mask (see DM ball). RDQS# is only used when RDQS is enabled and differential data

strobe mode is enabled.

VDD

VDDQ

VDDL

VREF

VSS

Supply

Supply

Supply

Supply

Supply

Supply

Supply

–

Power supply: 1.8V ±0.1V.

DQ power supply: 1.8V ±0.1V. Isolated on the device for improved noise immunity.

DLL power supply: 1.8V ±0.1V.

SSTL_18 reference voltage (VDDQ/2).

Ground.

VSSDL

VSSQ

NC

DLL ground: Isolated on the device from VSS and VSSQ.

DQ ground: Isolated on the device for improved noise immunity.

No connect: These balls should be left unconnected.

NF

No function: x8: these balls are used as DQ[7:4]; x4: they are no function.

–

NU

Not used: For x16 only. If EMR(E10) = 0, A8 and E8 are UDQS# and LDQS#. If EMR(E10) =

–

1, then A8 and E8 are not used.

NU

Not used: For x8 only. If EMR(E10) = 0, A2 and E8 are RDQS# and DQS#. If EMR(E10) = 1,

then A2 and E8 are not used.

–

–

RFU

Reserved for future use: Row address bits A13 (x16 only), A14, and A15.

PDF: 09005aef821ae8bf

1GbDDR2.pdf – Rev. T 02/10 EN

Micron Technology, Inc. reserves the right to change products or specifications without notice.

18

© 2004 Micron Technology, Inc. All rights reserved.

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]