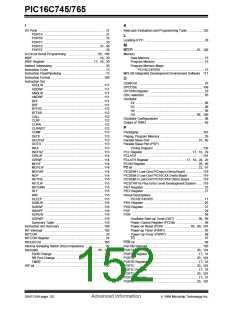

PIC16C745/765

PORTE Register ......................................................... 17, 38

Power-down Mode (SLEEP) ............................................ 107

Power-on Reset (POR)

Timing Diagram......................................................... 133

PR2 Register .............................................................. 18, 49

PRO MATE II Universal Programmer ........................... 119

Product Identification System .......................................... 159

Program Counter

PCLATH Register .................................................... 105

Program Memory

Paging ....................................................................... 29

Program Memory Maps

T

T1CKPS0 bit ..................................................................... 45

T1CKPS1 bit ..................................................................... 45

T1CON .............................................................................. 20

T1CON Register ......................................................... 19, 45

T1OSCEN bit .................................................................... 45

T1SYNC bit ....................................................................... 45

T2CKPS0 bit ..................................................................... 49

T2CKPS1 bit ..................................................................... 49

T2CON Register ......................................................... 19, 49

TAD .................................................................................... 93

Timer0

PIC16C745/765 ......................................................... 15

Program Verification ........................................................ 108

PSPMODE bit ...................................................... 37, 38, 40

PUSH ................................................................................. 29

RTCC ...................................................................... 101

Timing Diagram ....................................................... 134

Timer1

Timing Diagram ....................................................... 134

Timers

R

Timer0 ....................................................................... 43

External Clock ................................................... 44

Interrupt ............................................................. 43

Prescaler ........................................................... 44

Prescaler Block Diagram .................................. 43

T0CKI ................................................................ 44

T0IF ................................................................. 105

TMR0 Interrupt ................................................ 105

Timer1

Asynchronous Counter Mode ........................... 47

Capacitor Selection ........................................... 47

Operation in Timer Mode .................................. 46

Oscillator ........................................................... 47

Prescaler ........................................................... 47

Resetting of Timer1 Registers .......................... 47

Resetting Timer1 using a CCP Trigger Output . 47

Synchronized Counter Mode ............................ 46

T1CON .............................................................. 45

TMR1H .............................................................. 47

TMR1L .............................................................. 47

Timer2

RBIF bit ..................................................................... 33, 105

RCREG ................................................................................ 9

RCSTA Register ......................................................... 19, 76

RD pin ................................................................................ 40

Register File ...................................................................... 15

Registers

FSR Summary ........................................................... 19

INDF Summary .......................................................... 19

INTCON Summary .................................................... 19

PCL Summary ........................................................... 19

PCLATH Summary .................................................... 19

PORTB Summary ...................................................... 19

Reset Conditions ..................................................... 100

Special Function Register Summary ......................... 17

STATUS Summary .................................................... 19

TMR0 Summary ........................................................ 19

TRISB Summary ....................................................... 20

Reset .......................................................................... 95, 97

Timing Diagram ....................................................... 133

Reset Conditions for Special Registers ........................... 100

RP0 bit ........................................................................ 15, 22

RP1 bit ............................................................................... 22

RX9 bit ............................................................................... 76

RX9D bit ............................................................................ 76

Block Diagram ................................................... 49

Module .............................................................. 49

Postscaler ......................................................... 49

Prescaler ........................................................... 49

T2CON .............................................................. 49

Timing Diagrams

S

SEEVAL Evaluation and Programming System ........... 120

Services

USART Asynchronous Master Transmission ............ 80

USART Asynchronous Reception ............................. 81

USART Synchronous Reception ............................... 86

USART Synchronous Transmission .......................... 84

Wake-up from Sleep via Interrupt .................. 104, 108

Timing Diagrams and Specifications ............................... 130

A/D Conversion ....................................................... 139

Brown-out Reset (BOR) .......................................... 133

Capture/Compare/PWM (CCP) ............................... 135

CLKOUT and I/O ..................................................... 132

External Clock ......................................................... 130

Oscillator Start-up Timer (OST) .............................. 133

Parallel Slave Port (PSP) ........................................ 136

Power-up Timer (PWRT) ......................................... 133

Reset ....................................................................... 133

Timer0 and Timer1 .................................................. 134

USART Synchronous Receive ( Master/Slave) ....... 137

USART Synchronous Transmission

One-Time-Programmable (OTP) ................................. 7

Quick-Turnaround-Production (QTP) .......................... 7

Serialized Quick-Turnaround Production (SQTP) ....... 7

SLEEP ........................................................................ 95, 97

Software Simulator (MPLAB-SIM) ................................... 118

SPBRG Register ................................................................ 18

Special Features of the CPU ............................................. 95

Special Function Registers ................................................ 17

PIC16C745/765 ......................................................... 17

SPEN bit ............................................................................ 76

SREN bit ............................................................................ 76

SSPBUF ............................................................................ 19

Stack .................................................................................. 29

Overflows .................................................................. 29

Underflow .................................................................. 29

Status ................................................................................ 64

STATUS Register ..................................................... 22, 105

Synchronous Serial Port Module ....................................... 57

( Master/Slave) ........................................................ 137

Watchdog Timer (WDT) .......................................... 133

TMR0 ................................................................................ 20

TMR0 Register .................................................................. 17

TMR1CS bit ....................................................................... 45

1999 Microchip Technology Inc.

Advanced Information

DS41124A-page 153

MICROCHIP [ MICROCHIP ]

MICROCHIP [ MICROCHIP ]