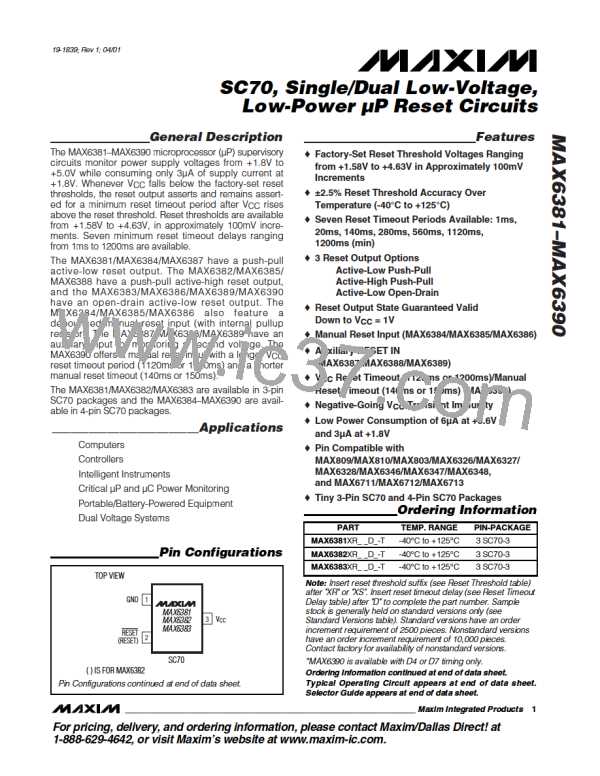

SC70, Single/Dual Low-Voltage,

Low-Power µP Reset Circuits

ELECTRICAL CHARACTERISTICS (continued)

(V

= full range, T = -40°C to +125°C, unless otherwise specified. Typical values are at T = +25°C.) (Note 1)

CC

A

A

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

µs

MR Minimum Input Pulse Width

MR Glitch Rejection

1

100

200

63

ns

MR to Reset Delay

ns

MAX6381–MAX6389

MAX6390

32

100

kΩ

Ω

MR Internal Pullup Resistance

800

1350

1.27

2300

1.295

1.308

1.321

T

T

T

= +25°C

1.245

1.232

1.219

A

A

A

Reset IN Input Threshold

V

V

= 0°C to +85°C

= -40°C to +125°C

THRST

V

V

falling at 4mV/µs from

RESETIN

RESET IN to RESET Delay

4.5

1

µs

+ 40mV to V

- 40mV

THRST

THRST

RESET IN Input Leakage Current

I

-50

+50

0.4

0.3

0.3

nA

RESETIN

V

V

V

≥ 4.5V, I

= 3.2mA, reset asserted

= 1.2mA, reset asserted

= 80µA, reset asserted

CC

CC

CC

SINK

SINK

SINK

Open-Drain RESET Output

Voltage

V

≥ 2.5V, I

≥ 1.0V, I

V

OL

Open-Drain RESET Output

Leakage Current

I

V

> V , RESET not asserted

1.0

µA

LKG

CC

TH

V

V

V

≥ 4.5V, I

≥ 2.5V, I

≥ 1.0V, I

= 3.2mA, reset asserted

= 1.2mA, reset asserted

= 80µA, reset asserted

0.4

0.3

0.3

CC

CC

CC

SINK

SINK

SINK

V

OL

Push-Pull RESET Output Voltage

V

✕

V

≥ 4.5V, I

= 800µA, reset not

0.8

CC

SOURCE

asserted

V

CC

V

V

OH

✕

V

≥ 2.5V, I

= 500µA, reset not

0.8

CC

SOURCE

asserted

V

CC

✕

0.8

V

V

V

≥ 4.5V, I

≥ 2.5V, I

≥ 1.8V, I

= 800µA, reset asserted

= 500µA, reset asserted

= 150µA, reset asserted

= 1µA, reset asserted

CC

CC

CC

SOURCE

SOURCE

SOURCE

SOURCE

V

CC

✕

0.8

V

CC

OH

✕

0.8

V

CC

Push-Pull RESET Output Voltage

V

✕

0.8

V

V

≥ 1.0V, I

CC

CC

V

CC

≥ 4.5V, I

= 3.2mA, reset not

SINK

0.4

0.3

asserted

V

OL

V

≥ 2.5V, I

= 1.2mA, reset not

CC

SINK

asserted

Note 1: Specifications over temperature are guaranteed by design, not production tested.

_______________________________________________________________________________________

3

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]