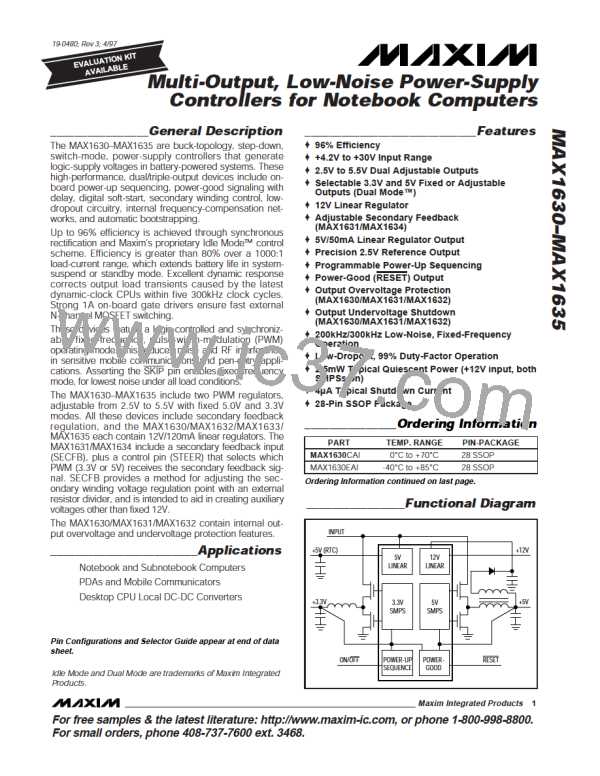

Mu lt i-Ou t p u t , Lo w -No is e P o w e r-S u p p ly

Co n t ro lle rs fo r No t e b o o k Co m p u t e rs

0–MAX1635

Rectifier Diode D3

2

PD(upper FET)= (I

)

x R

x DUTY

DS(ON)

LOAD

(Transformer Secondary Diode)

The secondary diode in coupled-inductor applications

mus t withs ta nd flyb a c k volta g e s g re a te r tha n 60V,

whic h us ua lly rule s out mos t Sc hottky re c tifie rs .

Common silicon rectifiers, such as the 1N4001, are also

prohibited because they are too slow. This often makes

fast silicon rectifiers such as the MURS120 the only

choice. The flyback voltage across the rectifier is relat-

V

x C

RSS

IN

+ V x I

x f x

+ 20ns

IN

LOAD

I

GATE

2

PD(lower FET) = (I

)

x R

x (1 - DUTY)

DS(ON)

LOAD

DUTY = (V

+ V ) / (V - V )

Q2 IN Q1

OUT

where: on-state voltage drop V = I

x R

DS(ON)

ed to the V - V

difference, according to the trans-

Q_

LOAD

IN

OUT

former turns ratio:

C

= MOSFET reverse transfer capacitance

RSS

I

= DH driver peak output current capabil-

ity (1A typical)

V

= V

+ (V - V

) x N

GATE

FLYBACK

SEC

IN OUT

20ns = DH driver inherent rise/fall time

where: N = the transformer turns ratio SEC/PRI

V

= the ma ximum s e c ond a ry DC outp ut

voltage

Under output short-circuit, the MAX1633/MAX1634/

MAX1635’s synchronous rectifier MOSFET suffers extra

stress because its duty factor can increase to greater

than 0.9. It may need to be oversized to tolerate a con-

tinuous DC s hort c irc uit. During s hort c irc uit, the

MAX1630/MAX1631/MAX1632’s output undervoltage

shutdown protects the synchronous rectifier under out-

put short-circuit conditions.

SEC

V

OUT

= the primary (main) output voltage

Subtract the main output voltage (V

in this equation if the secondary winding is returned to

and not to ground. The diode reverse breakdown

rating must also accommodate any ringing due to leak-

age inductance. D3’s current rating should be at least

twice the DC load current on the secondary output.

) from V

OUT FLYBACK

V

OUT

To reduce EMI, add a 0.1µF ceramic capacitor from the

high-side switch drain to the low-side switch source.

Lo w -Vo lt a g e Op e ra t io n

Low input voltages and low input-output differential

voltages each require extra care in their design. Low

absolute input voltages can cause the VL linear regula-

tor to enter dropout and eventually shut itself off. Low

input voltages relative to the output (low V -V

ferential) can cause bad load regulation in multi-output

flyback applications (see the design equations in the

Rectifier Clamp Diode

The rectifier is a clamp across the low-side MOSFET

that catches the negative inductor swing during the

60ns dead time between turning one MOSFET off and

each low-side MOSFET on. The latest generations of

MOSFETs incorporate a high-speed silicon body diode,

which serves as an adequate clamp diode if efficiency

is not of primary importance. A Schottky diode can be

placed in parallel with the body diode to reduce the for-

ward voltage drop, typically improving efficiency 1% to

2%. Use a diode with a DC current rating equal to one-

third of the load current; for example, use an MBR0530

(500mA-rated) type for loads up to 1.5A, a 1N5819 type

for loads up to 3A, or a 1N5822 type for loads up to

10A. The rectifier’s rated reverse breakdown voltage

must be at least equal to the maximum input voltage,

preferably with a 20% derating factor.

dif-

IN OUT

Transformer Design section). Also, low V -V

differ-

IN OUT

entials can also cause the output voltage to sag when

the load current changes abruptly. The amplitude of the

sag is a function of inductor value and maximum duty

factor (an Electrical Characteristics parameter, 98%

guaranteed over temperature at f = 200kHz), as follows:

2

(I

)

x L

x D

STEP

V

=

SAG

2 x C

x (V

- V

)

OUT

IN(MAX)

MAX OUT

Boost-Supply Diode D2

A signal diode such as a 1N4148 works well in most

applications. If the input voltage can go below +6V, use

a small (20mA) Schottky diode for slightly improved

efficiency and dropout characteristics. Don’t use large

power diodes, such as 1N5817 or 1N4001, since high

junction capacitance can pump up VL to excessive

voltages.

The cure for low-voltage sag is to increase the output

capacitor’s value. For example, at V = +5.5V, V

=

OUT

IN

+5V, L = 10µH, f = 200kHz, I

= 3A, a total capaci-

STEP

tance of 660µF keeps the sag less than 200mV. Note

that only the capacitance requirement increases, and

the ESR requirements don’t change. Therefore, the

added capacitance can be supplied by a low-cost bulk

capacitor in parallel with the normal low-ESR capacitor.

______________________________________________________________________________________ 21

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]