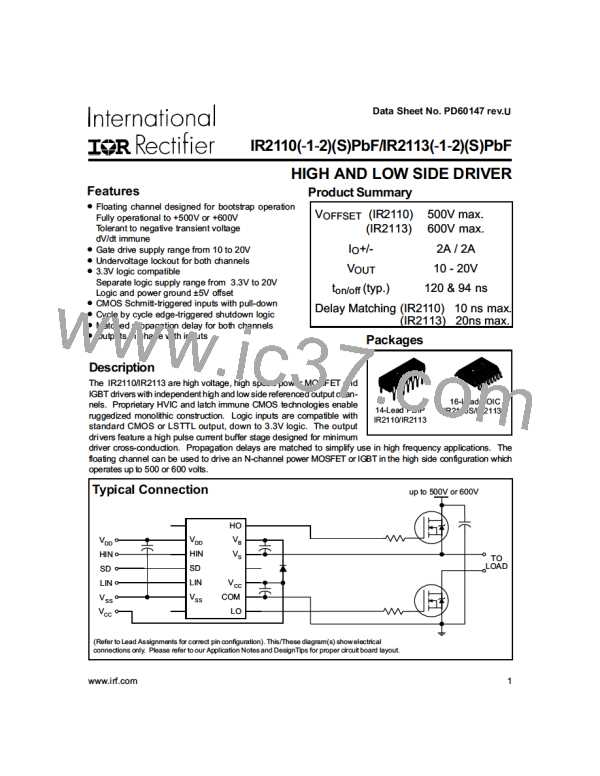

IR2110(-1-2)(S)PbF/IR2113(-1-2)(S)PbF

Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage param-

eters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured

under board mounted and still air conditions. Additional information is shown in Figures 28 through 35.

Symbol

Definition

High side floating supply voltage (IR2110)

(IR2113)

Min.

-0.3

Max.

525

Units

V

B

-0.3

625

V

S

High side floating supply offset voltage

High side floating output voltage

Low side fixed supply voltage

Low side output voltage

V

- 25

V

+ 0.3

+ 0.3

25

B

B

V

HO

V

S

- 0.3

V

B

V

CC

-0.3

-0.3

-0.3

V

V

LO

V

+ 0.3

CC

V

DD

Logic supply voltage

V

+ 25

+ 0.3

+ 0.3

SS

CC

DD

V

Logic supply offset voltage

V

- 25

V

V

SS

CC

V

Logic input voltage (HIN, LIN & SD)

Allowable offset supply voltage transient (figure 2)

V

- 0.3

IN

SS

dV /dt

s

—

50

V/ns

W

P

D

Package power dissipation @ T ≤ +25°C

A

(14 lead DIP)

—

—

—

—

—

-55

—

1.6

1.25

75

(16 lead SOIC)

(14 lead DIP)

(16 lead SOIC)

R

Thermal resistance, junction to ambient

THJA

°C/W

100

150

150

300

T

J

Junction temperature

°C

T

S

Storage temperature

T

L

Lead temperature (soldering, 10 seconds)

Recommended Operating Conditions

The input/output logic timing diagram is shown in figure 1. For proper operation the device should be used within the

recommended conditions. The V and V offset ratings are tested with all supplies biased at 15V differential. Typical

S SS

ratings at other bias conditions are shown in figures 36 and 37.

Symbol

Definition

High side floating supply absolute voltage

High side floating supply offset voltage

Min.

Max.

Units

V

B

V

S

+ 10

V + 20

S

V

S

(IR2110)

(IR2113)

Note 1

500

Note 1

600

V

High side floating output voltage

Low side fixed supply voltage

Low side output voltage

V

S

V

B

HO

V

10

0

20

CC

V

V

VCC

LO

V

Logic supply voltage

V

+ 3

V

+ 20

SS

DD

SS

V

Logic supply offset voltage

Logic input voltage (HIN, LIN & SD)

Ambient temperature

-5 (Note 2)

5

SS

V

V

V

DD

IN

SS

T

A

-40

125

°C

Note 1: Logic operational for V of -4 to +500V. Logic state held for V of -4V to -V . (Please refer to the Design Tip

S S BS

DT97-3 for more details).

Note 2: When V < 5V, the minimum V offset is limited to -V

DD.

DD

SS

2

www.irf.com

INFINEON [ Infineon ]

INFINEON [ Infineon ]