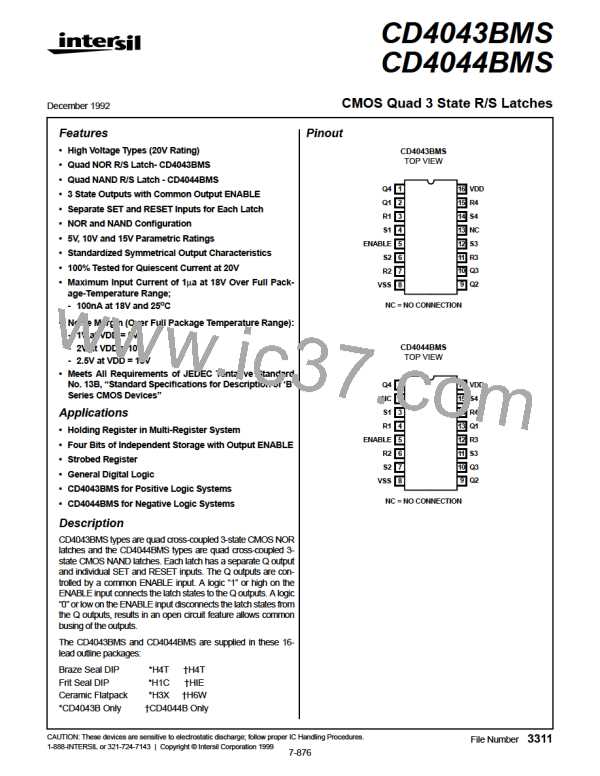

Specifications CD4043BMS, CD4044BMS

Functional Diagram

VDD

VDD

16

16

R1

S1

4

3

S1

R1

4

3

LATCH

1

LATCH

1

13 Q1

2

9

Q1

Q2

R2

S2

6

7

S2

R2

6

7

LATCH

2

LATCH

2

9

Q2

R3

S3

12

11

S3

R3

12

11

LATCH

3

LATCH

3

10 Q3

10 Q3

R4

S4

14

15

5

S4

R4

14

15

5

LATCH

4

LATCH

4

1

2

Q4

NC

1

Q4

ENABLE

ENABLE

13 NC

8

8

VSS

VSS

CD4043BMS

CD4044BMS

Logic Diagram

EQUIVALENT

NOR LATCH

EQUIVALENT

NAND LATCH

E

VDD

E

VDD

S1

S1

3

4

*

*

Q1

2

Q1

13

R1

R1

4

3

*

*

*

E

VSS

E

E

5

E

VSS

5

E

E

E

E

*

VDD

VDD

*ALL INPUTS ARE PROTECTED

BY CMOS PROTECTION

NETWORK

*ALL INPUTS ARE PROTECTED

BY CMOS PROTECTION

NETWORK

VSS

VSS

CD4043BMS

CD4044BMS

TRUTH TABLE

CD4043BMS

CD4044BMS

S

X

O

1

R

X

O

O

1

E

O

1

Q

OC*

NC**

1

S

X

1

R

X

1

E

O

1

Q

OC*

NC**

1

1

O

1

1

1

O

1

1

O

O

O

1

O

1

1

∆

O

1

∆∆

* Open Circuit

** No Change

* Open Circuit

** No Change

∆ Dominated by S = 1 input

∆∆ Dominated by R = O input

7-881

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]