8086

can occur between 8086 bus cycles. These are re-

ferred to as ‘‘Idle’’ states (T ) or inactive CLK cycles.

S

S

S

0

Characteristics

2

1

i

The processor uses these cycles for internal house-

keeping.

0 (LOW)

0

0

Interrupt Acknowledge

Read I/O

0

0

1

1

0

0

1

1

1

0

1

0

1

0

1

During T of any bus cycle the ALE (Address Latch

1

0

Write I/O

Enable) signal is emitted (by either the processor or

the 8288 bus controller, depending on the MN/MX

strap). At the trailing edge of this pulse, a valid ad-

dress and certain status information for the cycle

may be latched.

0

Halt

1 (HIGH)

Instruction Fetch

Read Data from Memory

Write Data to Memory

Passive (no bus cycle)

1

1

1

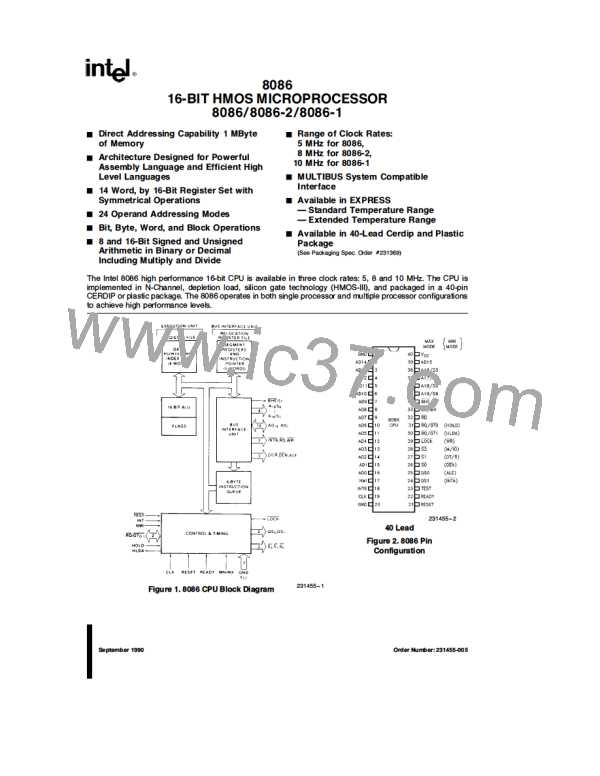

Status bits S , S , and S are used, in maximum

2

0

1

mode, by the bus controller to identify the type of

bus transaction according to the following table:

231455–8

Figure 5. Basic System Timing

9

INTEL [ INTEL ]

INTEL [ INTEL ]