TECHNICAL DATA

IN74HCT373A

Octal 3-State Noninverting

Transparent Latch

High-Performance Silicon-Gate CMOS

The IN74HCT373A may be used as a level converter for

interfacing TTL or NMOS outputs to High-Speed CMOS inputs.

The IN74HCT373A is identical in pinout to the LS/ALS373.

The eight latches of the IN74HCT373A are transparent D-type

latches. While the Latch Enable is high the Q outputs follow the Data

Inputs. When Latch Enable is taken low, data meeting the setup and

hold times becomes latched.

The Output Enable does not affect the state of the latch, but when

Output Enable is high, all outputs are forced to the high-impedance

state. Thus, data may be latched even when the outputs are not

enabled.

ORDERING INFORMATION

IN74HCT373AN Plastic

IN74HCT373ADW SOIC

TA = -55° to 125° C for all packages

•

•

•

•

TTL/NMOS-Compatible Input Levels

Outputs Directly Interface to CMOS, NMOS, and TTL

Operating Voltage Range: 4.5 to 5.5 V

Low Input Current: 1.0 µA

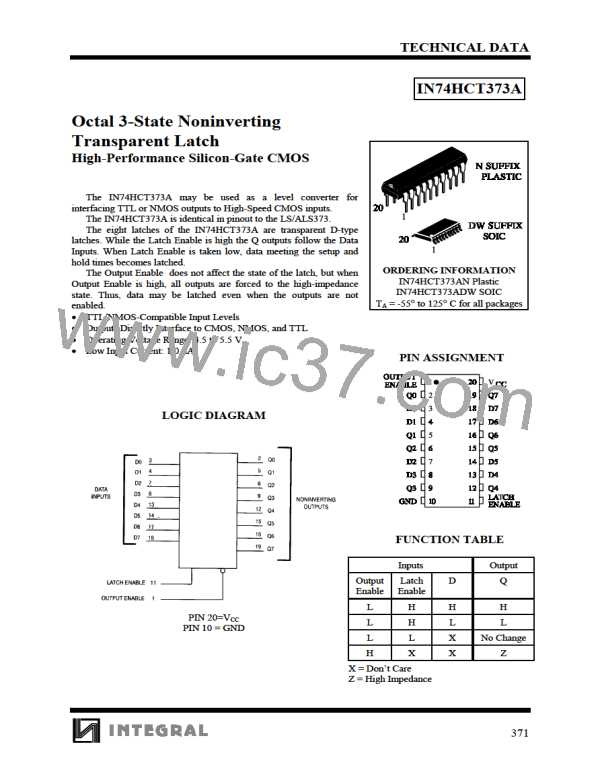

PIN ASSIGNMENT

LOGIC DIAGRAM

FUNCTION TABLE

Inputs

Latch

Output

Q

Output

D

Enable Enable

L

L

L

H

H

H

L

H

L

H

PIN 20=VCC

PIN 10 = GND

L

No Change

Z

X

X

X

X = Don’t Care

Z = High Impedance

371

INTEGRAL [ INTEGRAL CORP. ]

INTEGRAL [ INTEGRAL CORP. ]