IC42S16100

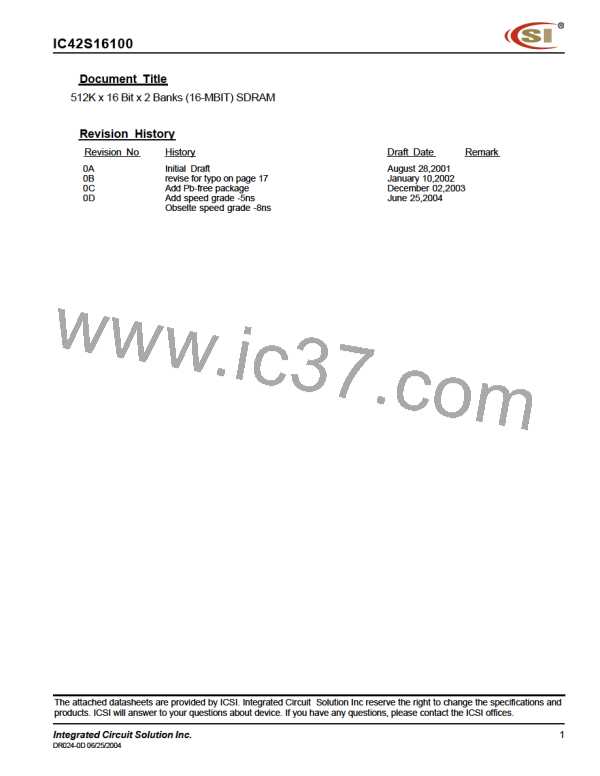

Read Cycle / Ping-Pong Operation (Bank Switching)

T0

T1

T2

T3

T4

T5

T6

T7

T8

T9

T10

CLK

t

CHI

t

CKS

t

CK

t

CL

CKE

CS

t

t

CKA

CH

t

CS

t

CS

tCH

tCH

tCH

RAS

t

t

CS

CS

CAS

WE

t

t

AS

AS

tAH

(1)

(1)

ROW

ROW

COLUMN

ROW

ROW

ROW

COLUMN

A0-A9

AUTO PRE

AUTO PRE

t

t

AH

AH

ROW

A10

A11

NO PRE

BANK 1

BANK 0 OR 1

BANK 0

BANK 0 OR 1

BANK 1

NO PRE

BANK 0

t

AS

BANK 0

BANK 0

BANK 1

t

CH

t

CS

t

QMD

DQM

t

AC

t

AC

t

AC

t

AC

t

OH

t

OH

t

OH

t

OH

DOUT 0m

D

OUT 0m+1

D

OUT 1m

D

OUT 1m+1

I/O

t

LZ

t

LZ

t

HZ

tHZ

t

RRD

(BANK 0 TO 1)

RCD

(BANK 0)

t

t

CAC

t

CAC

t

RCD

t

RCD

(BANK 0)

RAS

(BANK 0)

(BANK 1)

(BANK 1)

(BANK 1)

t

RP

(BANK 0)

t

t

RAS

(BANK 0)

t

RC

t

RC

(BANK 0)

(BANK 0)

t

RAS

t

RP

(BANK 1)

(BANK1)

t

RC

(BANK 1)

<ACT 0

>

<ACT1>

<

READ 0

READA 0

>

<

READ 1

READA 1>

>

<

PRE 0>

<

ACT 0>

<PRE 1>

<

>

<

Undefined

Don’t Care

CAS latency = 2, burst length = 2

Note 1: A8,A9 = Don't Care.

Integrated Circuit Solution Inc.

43

DR024-0D 06/25/2004

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]