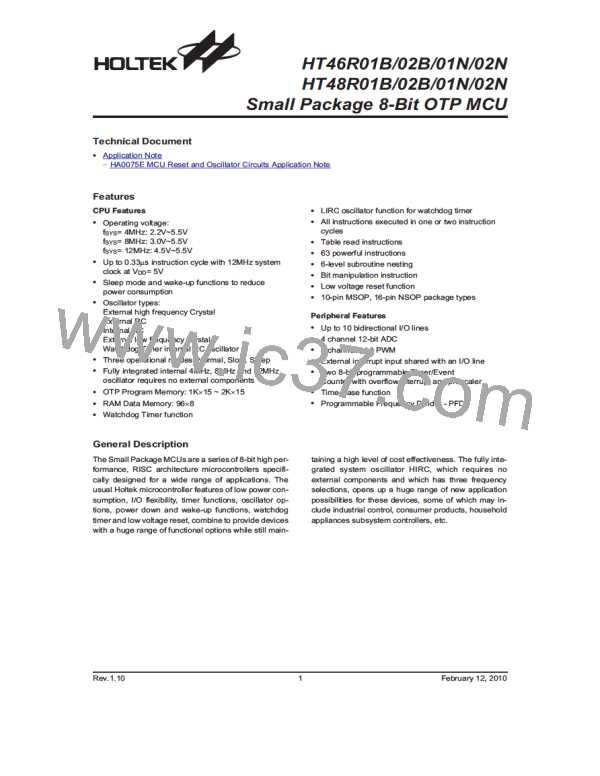

HT46R01B/02B/01N/02N

HT48R01B/02B/01N/02N

·

ADRH, ADRL Register

ADRH

ADRL

Bit

7

6

5

4

3

D7

R

2

D6

R

1

D5

R

0

D4

R

7

D3

R

6

D2

R

5

D1

R

4

D0

R

3

2

1

0

Name D11 D10 D9

D8

R

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

R/W

R

x

R

x

R

x

POR

x

x

x

x

x

x

x

x

x

²x² unknown

unimplemented, read as ²0²

D11~D0: ADC conversion data

·

ADCR Register

Bit

7

6

EOCB

R

5

PCR3

R/W

0

4

PCR2

R/W

0

3

2

1

0

ACS0

R/W

0

Name

R/W

START

R/W

0

PCR1

R/W

0

PCR0

R/W

0

ACS1

R/W

0

POR

1

Bit 7

START: Start the A/D conversion

0®1®0 : start

0®1

: reset the A/D converter and set EOCB to ²1²

Bit 6

EOCB: End of A/D conversion flag

0: A/D conversion ended

1: A/D conversion in progress

Bit 5~3

PCR3, PCR2, PCR1, PCR0: A/D channel configuration

0: I/O

1: analog input n (n=0~3)

If PCR0~PCR3 are all zero, the ADC circuit is power off to reduce power consumption

Bit 2~0

ACS1 ~ ACS0: Select A/D channel

00: AN0

01: AN1

10: AN2

11: AN3

Rev.1.10

44

February 12, 2010

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]