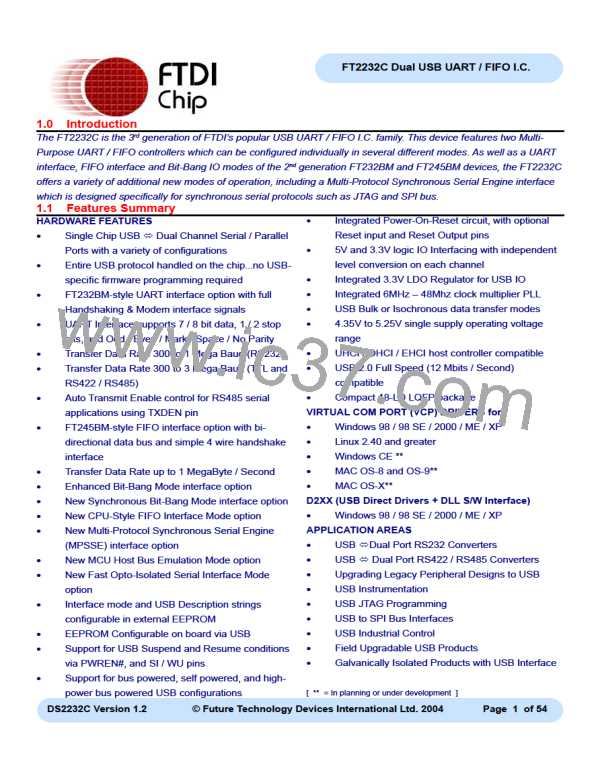

FT2232C Dual USB UART / FIFO I.C.

In addition to the BM chip features, the FT2232C incorporates the following new features and interface modes :-

•

Enhanced Asynchronous Bit-Bang Interface

The FT2232C supports FTDI’s BM chip Bit Bang

mode. In Bit Bang mode, the eight FIFO data lines

can be switched between FIFO interface mode and

an 8-bit Parallel IO port. Data packets can be sent

to the device and they will be sequentially sent to

the interface at a rate controlled by an internal timer

(equivalent to the baud rate prescaler). With the

FT2232C device this mode has been enhanced

so that the internal RD# and WR# strobes are now

brought out of the device which can be used to allow

external logic to be clocked by accesses to the Bit-

Bang IO bus.

can be configured for different industry standards, or

proprietary bus protocols. For instance, it is possible

to connect one of the FT2232C’s channels to an

SRAM configurable FPGA as supplied by vendors

such as Altera and Xilinx. The FPGA device would

normally be un-configured (i.e. have no defined

function) at power-up. Application software on the PC

could use the MPSSE to download configuration data

to the FPGA over USB. This data would define the

hardware’s function on power up. The other FT2232

channel would be available for other devices.

This approach would allow a customer to create a

“generic” USB peripheral, who’s hardware function

can be defined under control of the application

software. The FPGA based hardware could be easily

upgraded or totally changed simply by changing the

FPGA configuration data file. (See FTDI’s MORPH-

IC development module for a practicle example,

www.morph-ic.com)

•

•

•

Synchronous Bit-Bang Interface

Synchronous Bit-Bang Mode differs from

Asynchronous Bit-Bang mode in that the device

is only read when it is written to. Thus making it

easier for the controlling program to measure the

response to an output stimulus as the data returned

is synchronous to the output data.

•

MCU Host Bus Emulation

This new mode combines the ‘A’ and ‘B’ bus interface

to make the FT2232C interface emulate a standard

8048 / 8051 style MCU bus. This allows peripheral

devices for these MCU families to be directly

attached to the FT2232C with IO being performed

over USB with the help of MPSSE interface

technology.

High Output Drive Level Capabillity

The IO interface pins can be made to drive out at

three times the standard drive level thus allowing

multiple devices, or devices that require a greater

drive strength to be interfaced to the FT2232C. This

option is configured in the external EEPROM, ad can

be set individually for each channel.

•

Fast Opto-Isolated Serial Interface

CPU-Style FIFO Interface

A new proprietary FTDI protocol is designed to

allow galvanically isolated devices to communicate

sychronously with the FT2232C using just 4 signal

wires (over two dual opto-isolators), and two power

lines. The peripheral circuitry controls the data

transfer rate in both directions, whilst maintaining

full data integrity. Maximum USB full speed data

rates can be acheived. Both ‘A’ and ‘B’ channels

can communicate over the same 4 wire interface if

desired.

The CPU style FIFO interface is essentially the same

function as the classic FT245 interface, however the

bus signals have been redefined to make them easier

to interface to a CPU bus.

•

Multi-Protocol Synchronous Serial Engine

Interface (M.P.S.S.E.)

The Multi-Protocol Synchronous Serial Engine

(MPSSE) interface is a new option designed to

interface efficiently with synchronous serial protocols

such as JTAG and SPI Bus. It is very flexible in that it

DS2232C Version 1.2

© Future Technology Devices International Ltd. 2004

Page 5 of 54

FTDI [ FUTURE TECHNOLOGY DEVICES INTERNATIONAL LTD. ]

FTDI [ FUTURE TECHNOLOGY DEVICES INTERNATIONAL LTD. ]