xr

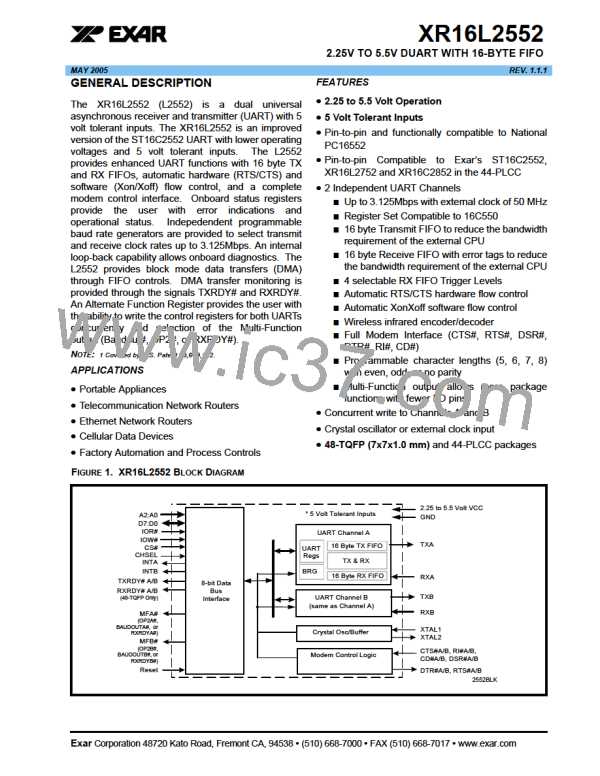

XR16L2552

2.25V TO 5.5V DUART WITH 16-BYTE FIFO

REV. 1.1.1

TABLE 13: UART RESET CONDITIONS FOR CHANNELS A AND B

REGISTERS

DLL

RESET STATE

Bits 7-0 = 0xXX

Bits 7-0 = 0xXX

Bits 7-0 = 0x00

Bits 7-0 = 0xXX

Bits 7-0 = 0xXX

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x01

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x60

Bits 3-0 = Logic 0

DLM

AFR

RHR

THR

IER

FCR

ISR

LCR

MCR

LSR

MSR

Bits 7-4 = Logic levels of the inputs inverted

SPR

EFR

Bits 7-0 = 0xFF

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

RESET STATE

Logic 1

XON1

XON2

XOFF1

XOFF2

I/O SIGNALS

TX

MF#

Logic 1

RTS#

Logic 1

DTR#

Logic 1

TXRDY#

INT

Logic 0

Logic 0

TYPICAL PACKAGE THERMAL RESISTANCE DATA (MARGIN OF ERROR: ± 15%)

theta-ja =59oC/W, theta-jc = 16oC/W

theta-ja = 50oC/W, theta-jc = 21oC/W

Thermal Resistance (48-TQFP)

Thermal Resistance (44-PLCC)

35

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]