XR16L2552

2.25V TO 5.5V DUART WITH 16-BYTE FIFO

xr

REV. 1.1.1

FIGURE 11. AUTO RTS AND CTS FLOW CONTROL OPERATION

Local UART

UARTA

Remote UART

UARTB

RXA

TXB

Receiver FIFO

Trigger Reached

Transmitter

RTSA#

TXA

CTSB#

RXB

Auto RTS

Trigger Level

Auto CTS

Monitor

Receiver FIFO

Trigger Reached

Transmitter

CTSA#

RTSB#

Auto CTS

Monitor

Auto RTS

Trigger Level

Assert RTS# to Begin

Transmission

1

10

11

ON

ON

ON

RTSA#

OFF

OFF

7

2

ON

3

CTSB#

TXB

8

Restart

9

Data Starts

6

Suspend

4

RXA FIFO

Receive

Data

RX FIFO

Trigger Level

RTS High

Threshold

RTS Low

Threshold

5

RX FIFO

Trigger Level

12

INTA

(RXA FIFO

Interrupt)

RTSCTS1

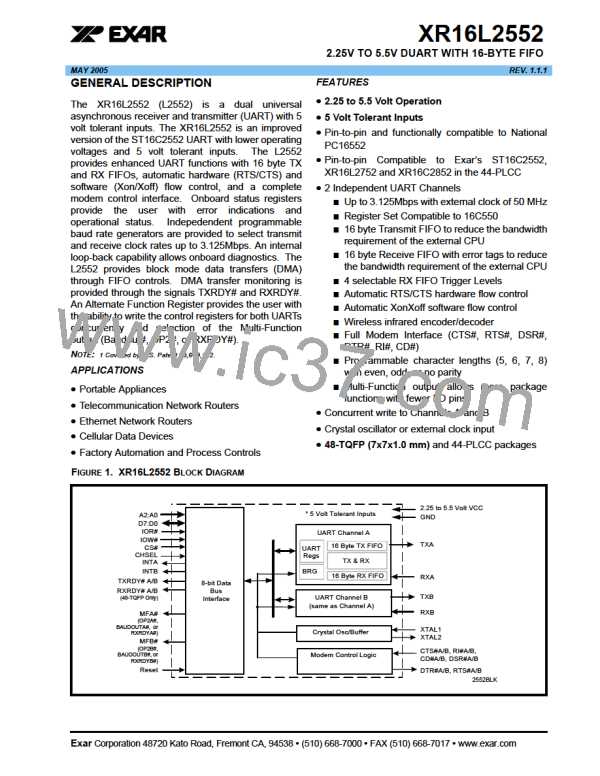

The local UART (UARTA) starts data transfer by asserting RTSA# (1). RTSA# is normally connected to CTSB# (2) of

remote UART (UARTB). CTSB# allows its transmitter to send data (3). TXB data arrives and fills UARTA receive FIFO

(4). When RXA data fills up to its receive FIFO trigger level, UARTA activates its RXA data ready interrupt (5) and con-

tinues to receive and put data into its FIFO. If interrupt service latency is long and data is not being unloaded, UARTA

monitors its receive data fill level to match the upper threshold of RTS delay and de-assert RTSA# (6). CTSB# follows

(7) and request UARTB transmitter to suspend data transfer. UARTB stops or finishes sending the data bits in its trans-

mit shift register (8). When receive FIFO data in UARTA is unloaded to match the lower threshold of RTS delay (9),

UARTA re-asserts RTSA# (10), CTSB# recognizes the change (11) and restarts its transmitter and data flow again until

next receive FIFO trigger (12). This same event applies to the reverse direction when UARTA sends data to UARTB

with RTSB# and CTSA# controlling the data flow.

16

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]