3D7225

APPLICATION NOTES (CONT’D)

custom reference designator identifying the

intended frequency and duty cycle of operation.

The programmed delay accuracy of the device is

guaranteed, therefore, only for the user specified

input characteristics. Small input pulse width

variation about the selected pulse width will only

marginally impact the programmed delay

accuracy, if at all. Nevertheless, it is strongly

recommended that the engineering staff at DATA

DELAY DEVICES be consulted.

circuitry to minimize the delay variations induced

by fluctuations in power supply and/or

temperature.

The thermal coefficient is reduced to 250 PPM/C,

which is equivalent to a variation, over the -40C

to 85C operating range, of ±2% from the room-

temperature delay settings and/or 1.0ns,

whichever is greater. The power supply

coefficient is reduced, over the 4.75V-5.25V

operating range, to ±1% of the delay settings at

the nominal 5.0VDC power supply and/or 1.0ns,

whichever is greater. It is essential that the

power supply pin be adequately bypassed

and filtered. In addition, the power bus

should be of as low an impedance

POWER SUPPLY AND

TEMPERATURE CONSIDERATIONS

The delay of CMOS integrated circuits is strongly

dependent on power supply and temperature.

The monolithic 3D7225 programmable delay line

utilizes novel and innovative compensation

construction as possible. Power planes are

preferred.

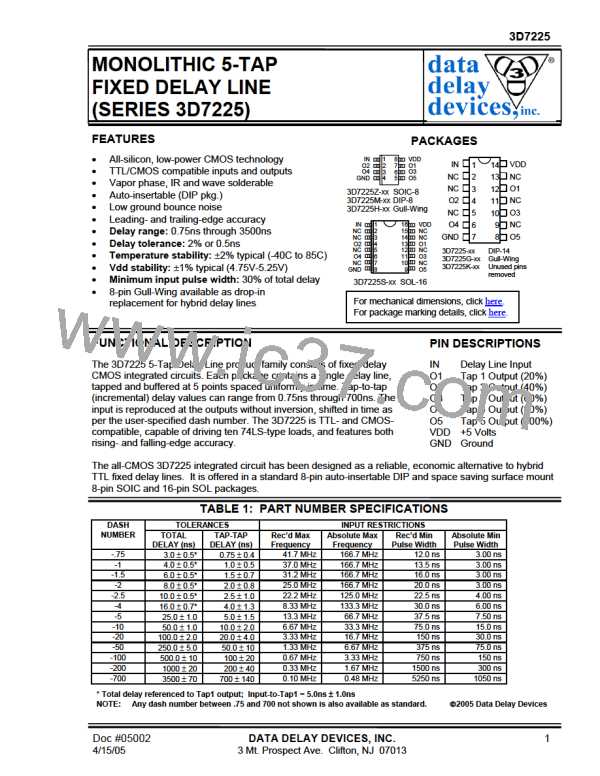

DEVICE SPECIFICATIONS

TABLE 2: ABSOLUTE MAXIMUM RATINGS

PARAMETER

DC Supply Voltage

Input Pin Voltage

Input Pin Current

Storage Temperature

Lead Temperature

SYMBOL

VDD

MIN

-0.3

-0.3

-1.0

-55

MAX

7.0

UNITS NOTES

V

V

VIN

VDD+0.3

1.0

IIN

TSTRG

TLEAD

mA

C

25C

150

300

C

10 sec

TABLE 3: DC ELECTRICAL CHARACTERISTICS

(-40C to 85C, 4.75V to 5.25V)

PARAMETER

SYMBOL

MIN

TYP

MAX

UNITS

mA

V

NOTES

Static Supply Current*

High Level Input Voltage

Low Level Input Voltage

High Level Input Current

Low Level Input Current

IDD

VIH

VIL

IIH

3.5

5.5

2.0

0.8

1.0

1.0

-4.0

V

VIH = VDD

VIL = 0V

µA

IIL

IOH

µA

High Level Output

-35.0

15.0

2.0

mA

VDD = 4.75V

Current

V

OH = 2.4V

Low Level Output Current

IOL

4.0

mA

ns

VDD = 4.75V

VOL = 0.4V

CLD = 5 pf

Output Rise & Fall Time

TR & TF

2.5

*IDD(Dynamic) = 5 * CLD * VDD * F

Input Capacitance = 10 pf typical

Output Load Capacitance (CLD) = 25 pf max

where: CLD = Average capacitance load/tap (pf)

F = Input frequency (GHz)

Doc #05002

4/15/05

DATA DELAY DEVICES, INC.

3 Mt. Prospect Ave. Clifton, NJ 07013

3

DATADELAY [ DATA DELAY DEVICES, INC. ]

DATADELAY [ DATA DELAY DEVICES, INC. ]