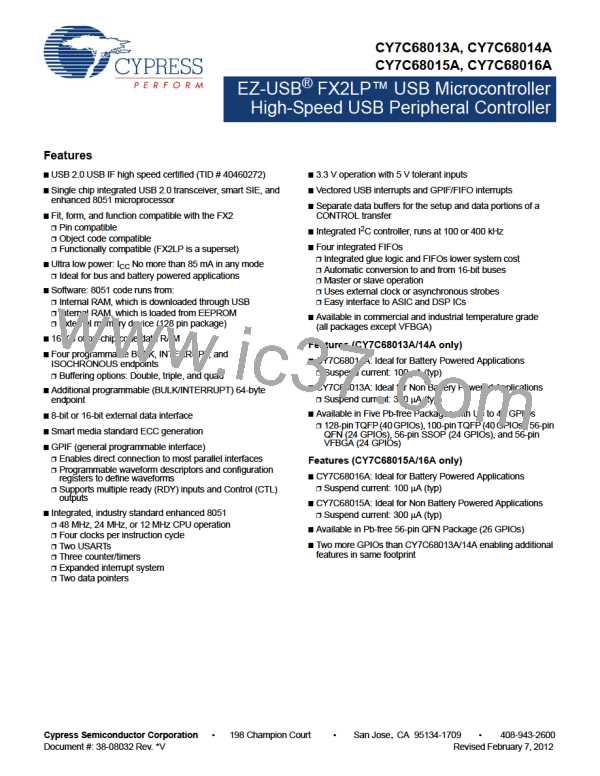

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

2

For designers migrating from the FX2 to the FX2LP a change in

the bill of material and review of the memory allocation (due to

increased internal memory) is required. For more information

about migrating from EZ-USB FX2 to EZ-USB FX2LP, see the

application note titled Migrating from EZ-USB FX2 to EZ-USB

FX2LP available in the Cypress web site.

2.18 I C Controller

FX2LP has one I2C port that is driven by two internal controllers,

one that automatically operates at boot time to load VID/PID/DID

and configuration information, and another that the 8051 uses

when running to control external I2C devices. The I2C port

operates in master mode only.

Table 8. Part Number Conversion Table

2.18.1 I2C Port Pins

EZ-USB FX2

Part Number

EZ-USB FX2LP

Part Number

Package

Description

The I2C pins SCL and SDA must have external 2.2 k pull up

resistors even if no EEPROM is connected to the FX2LP.

External EEPROM device address pins must be configured

properly. See Table 7 for configuring the device address pins.

CY7C68013-56PVC CY7C68013A-56PVXC or 56-pin

CY7C68014A-56PVXC SSOP

CY7C68013-56PVCT CY7C68013A-56PVXCTor 56-pin

Table 7. Strap Boot EEPROM Address Lines to These Values

CY7C68014A-56PVXCT SSOP –

Bytes

16

Example EEPROM

24LC00[9]

24LC01

A2

N/A

0

A1

N/A

0

A0

N/A

0

Tape and

Reel

CY7C68013-56LFC CY7C68013A-56LFXC or 56-pin QFN

CY7C68014A-56LFXC

128

256

4K

24LC02

0

0

0

CY7C68013-100AC CY7C68013A-100AXC or 100-pin

24LC32

0

0

1

CY7C68014A-100AXC

CY7C68013-128AC CY7C68013A-128AXC or 128-pin

CY7C68014A-128AXC TQFP

TQFP

8K

24LC64

0

0

1

16K

24LC128

0

0

1

2.18.2 I2C Interface Boot Load Access

2.20 CY7C68013A/14A and CY7C68015A/16A

Differences

At power on reset the I2C interface boot loader loads the

VID/PID/DID configuration bytes and up to 16 KBytes of

program/data. The available RAM spaces are 16 KBytes from

0x0000–0x3FFF and 512 bytes from 0xE000–0xE1FF. The 8051

is in reset. I2C interface boot loads only occur after power on

reset.

CY7C68013A is identical to CY7C68014A in form, fit, and

functionality. CY7C68015A is identical to CY7C68016A in form,

fit, and functionality. CY7C68014A and CY7C68016A have a

lower suspend current than CY7C68013A and CY7C68015A

respectively and are ideal for power sensitive battery

applications.

2.18.3 I2C Interface General-Purpose Access

CY7C68015A and CY7C68016A are available in 56-pin QFN

package only. Two additional GPIO signals are available on the

CY7C68015A and CY7C68016A to provide more flexibility when

neither IFCLK or CLKOUT are needed in the 56-pin package.

The 8051 can control peripherals connected to the I2C bus using

the I2CTL and I2DAT registers. FX2LP provides I2C master

control only, it is never an I2C slave.

2.19 Compatible with Previous Generation

EZ-USB FX2

USB developers wanting to convert their FX2 56-pin application

to a bus-powered system directly benefit from these additional

signals. The two GPIOs give developers the signals they need

for the power control circuitry of their bus-powered application

without pushing them to a high pincount version of FX2LP.

The EZ-USB FX2LP is form, fit and with minor exceptions

functionally compatible with its predecessor, the EZ-USB FX2.

This makes for an easy transition for designers wanting to

upgrade their systems from the FX2 to the FX2LP. The pinout

and package selection are identical and a vast majority of

firmware previously developed for the FX2 functions in the

FX2LP.

The CY7C68015A is only available in the 56-pin QFN package

Table 9. CY7C68013A/14A and CY7C68015A/16A

Pin Differences

CY7C68013A/CY7C68014A CY7C68015A/CY7C68016A

IFCLK

PE0

PE1

CLKOUT

Note

9. This EEPROM does not have address pins.

Document #: 38-08032 Rev. *V

Page 14 of 66

CYPRESS [ CYPRESS ]

CYPRESS [ CYPRESS ]