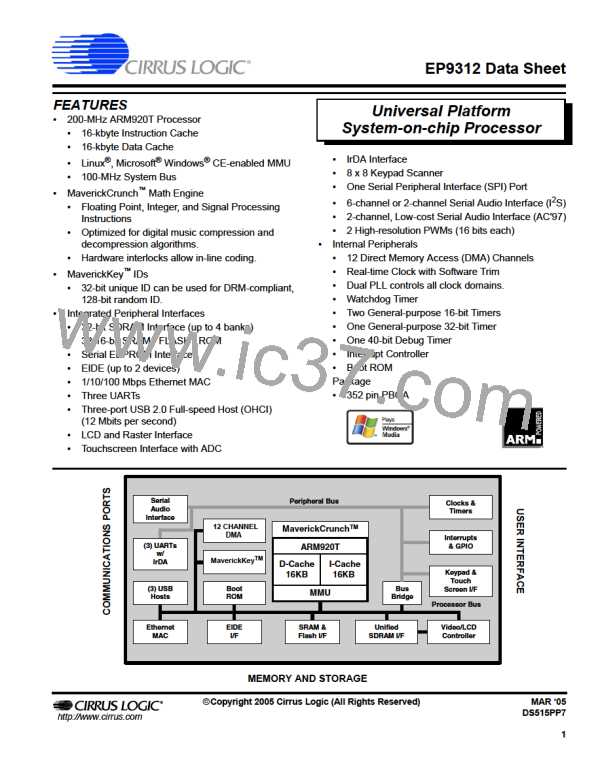

EP9312

Universal Platform SOC Processor

t2CYCRD

tCYCRD

tCYCRD

t2CYCRD

DSTROBE

(device)

tDVH

tDVS

tDVH

tDVS

tDVH

DD (15:0)

(device)

DSTROBE

(host)

tDH

tDS

tDH

tDS

tDH

DD (15:0)

(host)

Note: DD (15:0) and DSTROBE signals are shown at both the host and the device to emphasize that cable settling time as well as

cable propagation delay shall not allow the data signals to be considered stable at the host until some time after they are driven

by the device.

Figure 20. Sustained Ultra DMA data-in Burst

DMARQ

(device)

DMACKn

(host)

tRP

STOP

(host)

tSR

HDMARDYn

(host)

tRFS

DSTROBE

(device)

DD(15:0)

(device)

Figure 21. Host Pausing an Ultra DMA data-in Burst

36

©Copyright 2005 Cirrus Logic (All Rights Reserved)

DS515PP7

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]