pins. A time delay of approximately 400 ms is required after applying power to the device or after exiting

a reset state. During this voltage reference ramp delay, all serial ports and DAC outputs will be automat-

ically muted.

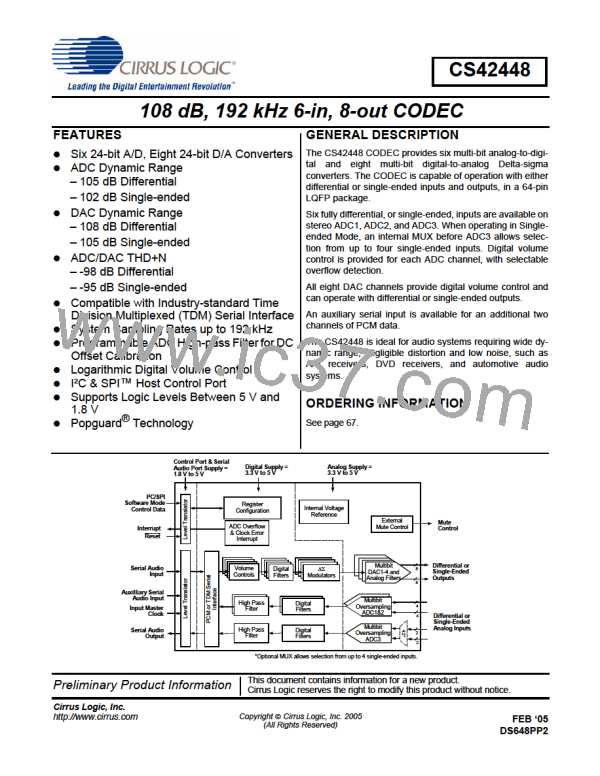

4.11 Power Supply, Grounding, and PCB layout

As with any high resolution converter, the CS42448 requires careful attention to power supply and ground-

ing arrangements if its potential performance is to be realized. Figure 1 shows the recommended power

arrangements, with VA connected to clean supplies. VD, which powers the digital circuitry, may be run

from the system logic supply. Alternatively, VD may be powered from the analog supply via a ferrite bead.

In this case, no additional devices should be powered from VD.

Extensive use of power and ground planes, ground plane fill in unused areas and surface mount decou-

pling capacitors are recommended. Decoupling capacitors should be as near to the pins of the CS42448

as possible. The low value ceramic capacitor should be the nearest to the pin and should be mounted on

the same side of the board as the CS42448 to minimize inductance effects. All signals, especially clocks,

should be kept away from the ADC/DAC_FILT+, VQ pins in order to avoid unwanted coupling into the

modulators. The ADC/DAC_FILT+ and VQ decoupling capacitors, particularly the 0.1 µF, must be posi-

tioned to minimize the electrical path from ADC/DAC_FILT+ and AGND. The CDB42448 evaluation board

demonstrates the optimum layout and power supply arrangements.

For optimal heat dissipation from the package, it is recommended that the area directly under the part be

filled with copper and tied to the ground plane. The use of vias connecting the topside ground to the back-

side ground is also recommended.

DS648PP2

41

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]