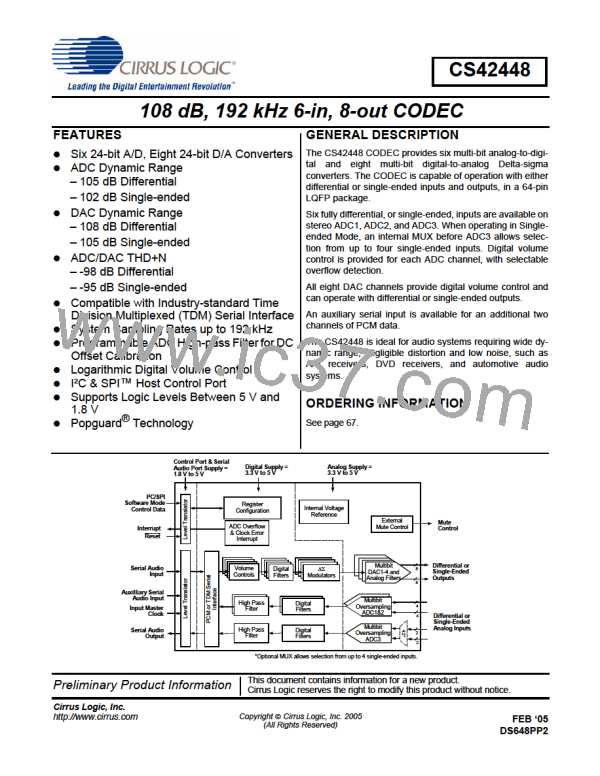

SWITCHING SPECIFICATIONS - ADC/DAC PORT (Inputs: Logic 0 = DGND, Logic 1 = VLS,

ADC_SDOUT C

= 15 pF.)

LOAD

Parameters (Note 20)

Symbol

Min

Max

Units

Slave Mode

RST pin Low Pulse Width

MCLK Frequency

(Note 16)

(Note 17)

1

-

ms

MHz

%

0.512

45

50

55

MCLK Duty Cycle

Input Sample Rate (LRCK)

Single-Speed Mode

Double-Speed Mode (Note 18)

Quad-Speed Mode (Note 19)

F

F

F

4

50

100

50

100

200

kHz

kHz

kHz

s

s

s

LRCK Duty Cycle

SCLK Duty Cycle

SCLK High Time

SCLK Low Time

45

45

8

55

55

-

%

%

t

ns

ns

ns

sckh

t

8

-

sckl

LRCK Rising Edge to SCLK Rising Edge

t

5

-

fss

t

t

lcks

SCLK Rising Edge to LRCK Falling Edge

t

16

-

-

35

-

ns

ns

ns

ns

ns

ns

ns

fsh

SCLK Falling Edge to ADC_SDOUT Output Valid

DAC_SDIN Setup Time Before SCLK Rising Edge

DAC_SDIN Hold Time After SCLK Rising Edge

DAC_SDIN Hold Time After SCLK Rising Edge

ADC_SDOUT Hold Time After SCLK Rising Edge

ADC_SDOUT Valid Before SCLK Rising Edge

dpd

t

3

ds

t

5

-

dh

t

t

5

-

dh1

dh2

dval

10

15

-

t

-

LRCK

LRCK

(input)

tlcks

tsckh

tsckl

tfsh

tfss

tsckh

tsckl

SCLK

SCLK

(input)

tds

tdh

MSB

tds

tdh1

MSB

DAC_SDINx

ADC_SDOUTx

MSB-1

MSB-1

DAC_SDIN1

MSB-1

tdpd

tdh2

tdval

MSB-1

MSB

ADC_SDOUT1

MSB

Figure 4. Serial Audio Interface Slave Mode Timing

Figure 5. TDM Serial Audio Interface Timing

20

DS648PP2

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]