PCM3793A

PCM3794A

www.ti.com

SLAS529A–JANUARY 2007–REVISED FEBRUARY 2007

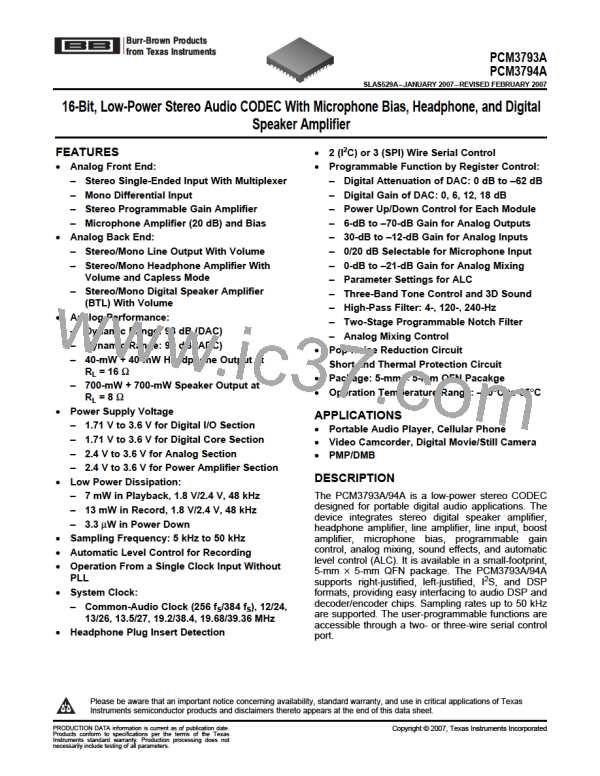

Registers 84–86

B15

B14

IDX6

IDX6

IDX6

B13

IDX5

IDX5

IDX5

B12

IDX4

IDX4

IDX4

B11

IDX3

IDX3

IDX3

B10

IDX2

IDX2

IDX2

B9

B8

B7

B6

B5

B4

B3

B2

B1

B0

Register 84

Register 85

Register 86

0

IDX1

IDX1

IDX1

IDX0

IDX0

IDX0

RSV

RSV

RSV

MSR2

RSV

NPR5

RSV

NPR4

RSV

MSTR

NPR2

RSV

RSV

NPR1

RSV

BIT0

NPR0

ZCRS

0

SRST

MBST

NPR3

ATOD

0

MSR1 MSR0

IDX[6:0]: 101 0100b (54h): Register 84

IDX[6:0]: 101 0101b (55h): Register 85

IDX[6:0]: 101 0110b (56h): Register 86

MSTR: Master or Slave Selection for Audio Interface

Default value: 0

This bit is used to select either master or slave mode for the audio interface. In master mode, the

PCM3793A/94A generates LRCK and BCK from the system clock. In slave mode, it receives LRCK and BCK

from another device.

MSTR = 0

MSTR = 1

Slave interface (default)

Master interface

BIT0: Bit Length Selection for Audio Interface

Default value: 1

This bit is used to select the data bit length for DAC input.

BIT0 = 0

BIT0 = 1

Reserved

16 bits (default)

SRST: System Reset

Default value: 0

This bit is used to enable system reset. All circuits are reset by setting SRST = 1. After completing the reset

sequence, SRST is set to 0 automatically.

SRST = 0

SRST = 1

Reset disabled (default)

Reset enabled

NPR[5:0]: System Clock Rate Selection

Default value: 000000

MSR[2:0]: System Clock Dividing Rate Selection in Master Mode (Register 70)

Default value: 000

These bits are used to select the system clock rate and the dividing rate of the input system clock. See Table 12

for the details.

46

Submit Documentation Feedback

BB [ BURR-BROWN CORPORATION ]

BB [ BURR-BROWN CORPORATION ]