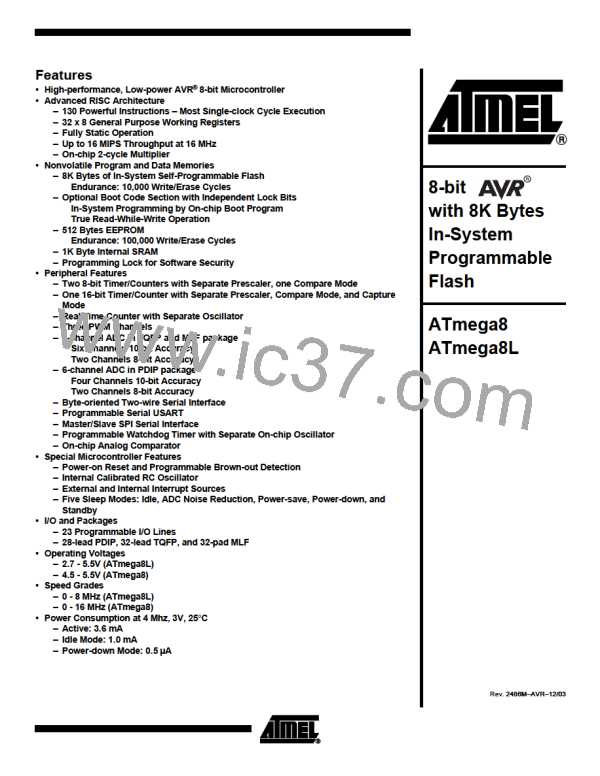

Figure 51. Phase Correct PWM Mode, Timing Diagram

OCn Interrupt Flag Set

OCRn Update

TOVn Interrupt Flag Set

TCNTn

(COMn1:0 = 2)

(COMn1:0 = 3)

OCn

OCn

1

2

3

Period

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches BOT-

TOM. The Interrupt Flag can be used to generate an interrupt each time the counter

reaches the BOTTOM value.

In phase correct PWM mode, the compare unit allows generation of PWM waveforms on

the OC2 pin. Setting the COM21:0 bits to 2 will produce a non-inverted PWM. An

inverted PWM output can be generated by setting the COM21:0 to 3 (see Table 45 on

page 116). The actual OC2 value will only be visible on the port pin if the data direction

for the port pin is set as output. The PWM waveform is generated by clearing (or setting)

the OC2 Register at the Compare Match between OCR2 and TCNT2 when the counter

increments, and setting (or clearing) the OC2 Register at Compare Match between

OCR2 and TCNT2 when the counter decrements. The PWM frequency for the output

when using phase correct PWM can be calculated by the following equation:

f

clk_I/O

f

= -----------------

OCnPCPWM

N 510

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2 Register represent special cases when generating a

PWM waveform output in the phase correct PWM mode. If the OCR2 is set equal to

BOTTOM, the output will be continuously low and if set equal to MAX the output will be

continuously high for non-inverted PWM mode. For inverted PWM the output will have

the opposite logic values.

At the very start of period 2 in Figure 51 OCn has a transition from high to low even

though there is no Compare Match. The point of this transition is to guarantee symmetry

around BOTTOM. There are two cases that give a transition without Compare Match:

•

OCR2A changes its value from MAX, like in Figure 51. When the OCR2A value is

MAX the OCn pin value is the same as the result of a down-counting Compare

Match. To ensure symmetry around BOTTOM the OCn value at MAX must

correspond to the result of an up-counting Compare Match.

112

ATmega8(L)

2486M–AVR–12/03

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]