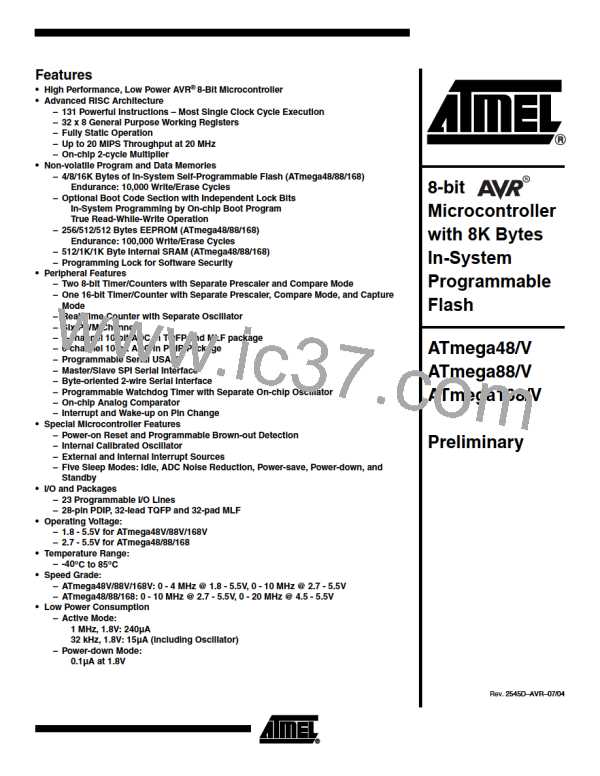

ATmega48/88/168

Asynchronous Timer Clock –

clkASY

The Asynchronous Timer clock allows the Asynchronous Timer/Counter to be clocked

directly from an external clock or an external 32 kHz clock crystal. The dedicated clock

domain allows using this Timer/Counter as a real-time counter even when the device is

in sleep mode.

ADC Clock – clkADC

The ADC is provided with a dedicated clock domain. This allows halting the CPU and

I/O clocks in order to reduce noise generated by digital circuitry. This gives more accu-

rate ADC conversion results.

Clock Sources

The device has the following clock source options, selectable by Flash Fuse bits as

shown below. The clock from the selected source is input to the AVR clock generator,

and routed to the appropriate modules.

Table 4. Device Clocking Options Select(1)

Device Clocking Option

Low Power Crystal Oscillator

Full Swing Crystal Oscillator

Low Frequency Crystal Oscillator

Internal 128 kHz RC Oscillator

Calibrated Internal RC Oscillator

External Clock

CKSEL3..0

1111 - 1000

0111 - 0110

0101 - 0100

0011

0010

0000

Reserved

0001

Note:

1. For all fuses “1” means unprogrammed while “0” means programmed.

Default Clock Source

The device is shipped with internal RC oscillator at 8.0MHz and with the fuse CKDIV8

programmed, resulting in 1.0MHz system clock. The startup time is set to maximum and

time-out period enabled. (CKSEL = "0010", SUT = "10", CKDIV8 = "0"). The default set-

ting ensures that all users can make their desired clock source setting using any

available programming interface.

Clock Startup Sequence

Any clock source needs a sufficient VCC to start oscillating and a minimum number of

oscillating cycles before it can be considered stable.

To ensure sufficient VCC, the device issues an internal reset with a time-out delay (tTOUT

)

after the device reset is released by all other reset sources. “System Control and Reset”

on page 40 describes the start conditions for the internal reset. The delay (tTOUT) is

timed from the Watchdog Oscillator and the number of cycles in the delay is set by the

SUTx and CKSELx fuse bits. The selectable delays are shown in Table 5. The fre-

quency of the Watchdog Oscillator is voltage dependent as shown in

“ATmega48/88/168 Typical Characteristics – Preliminary Data” on page 298.

Table 5. Number of Watchdog Oscillator Cycles

Typ Time-out (VCC = 5.0V)

Typ Time-out (VCC = 3.0V)

Number of Cycles

0

0 ms

4.1 ms

65 ms

0 ms

4.3 ms

69 ms

4K (4,096)

8K (8,192)

Main purpose of the delay is to keep the AVR in reset until it is supplied with minimum

V

CC. The delay will not monitor the actual voltage and it will be required to select a delay

25

2545D–AVR–07/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]