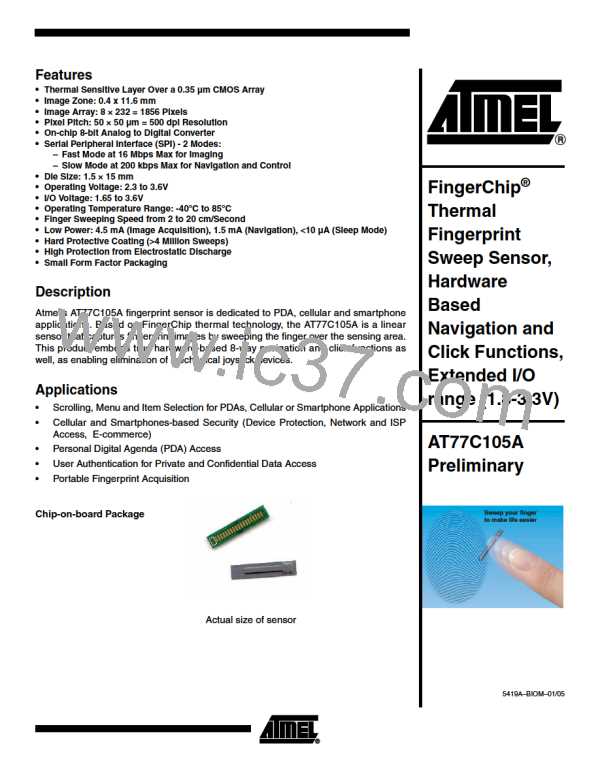

Sensor and Block Diagram

Figure 7. Functional Block Diagram

FPL

VDDA

GNDA

VDDD

GNDD

RST

VDD_IO

FSS

SCK

Fast Serial

Interface

SPI

Acquisition

(8-16 MHz)

Pixel Array

(232 x 8)

Array

CTRL

Navigation

Algorithms

MISO

Slow Serial

Interface

SPI

(200 kHz)

+

Oscillator (420 kHz)

MOSI

SSS

Click

Algorithm

Click

CTRL

Click Pixels

(12)

Control

Register

IRQ

Watchdog

Heating

SCANEN

TESTA

Test

The circuit is divided into the following main sections:

•

•

•

•

•

•

An array or frame of 8 × 232 pixels + 1 dummy column

An analog to digital converter

An on-chip oscillator

Control and status registers

Navigation and click units

Slow and fast serial interfaces

12

AT77C105A [Preliminary]

5419A–BIOM–01/05

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]