ASAHI KASEI

[AK4115]

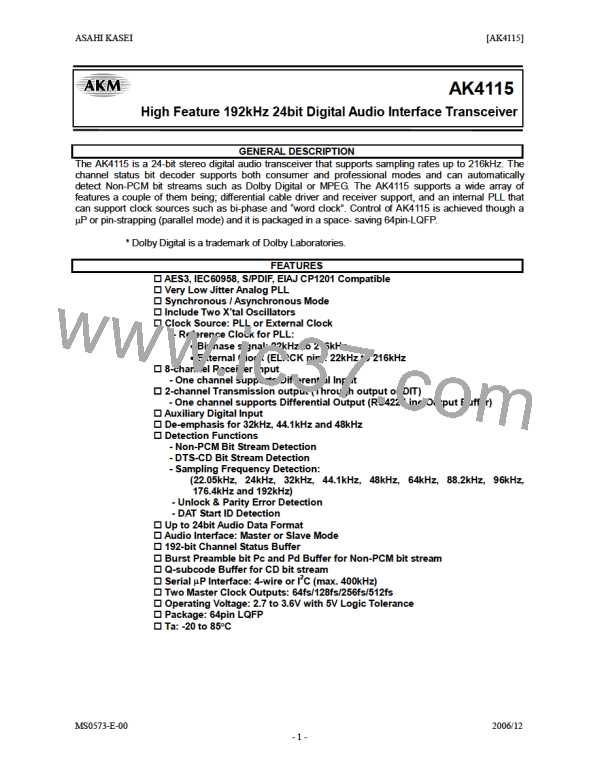

Clock Control

Addr

0AH Clock Control

R/W

Register Name

D7

TX1NE

R/W

1

D6

0

RD

0

D5

D4

D3

D2

WSYNC

R/W

0

D1

XSEL

R/W

0

D0

PSEL

R/W

0

MCK1E MCK1E ASYNC

R/W

1

R/W

1

R/W

0

Default

PSEL: Setting of PLL reference clock (See Table 1)

XSEL: Setting of X’tal oscillator (See Table 12)

WSYNC: Synchronization between the biphase signal and ELRCK

0: Disable (Default)

1: Enable

ASYNC: Setting of synchronous / asynchronous mode for DIT/DIR

0: Synchronous mode (Default)

1: Asynchronous mode

MCK1E: Setting of MCKO1 output

0: Disable. Output “L”.

1: Enable (Default)

MCK2E: Setting of MCKO2 output

0: Disable. Output “L”.

1: Enable (Default)

TX1NE: Setting of TXN1 pin.

0: Disable. Output “L”. This mode is useful for consumer.

1: Enable (Default)

TX Control

Addr

Register Name

D7

D6

D5

D4

D3

D2

D1

D0

VTX

R/W

0

0BH TX Control

MSEL ECKS1 ECKS0 EDIF1 EDIF0 CTRAN CCRE

RD

0

R/W

Default

RD

0

R/W

1

R/W

1

R/W

0

R/W

0

R/W

1

VTX: Setting of Validity bit for TX

0: Valid (Default)

1: Invalid

CCRE: CCRC Enable at professional mode

0: CCRC data is not generated.

1: CCRC data is generated in professional mode. In consumer mode, CCRC data is not generated.

(Default)

CTRAN: Transfer mode of CR191-0 bits

0: Not transfer or finish to transfer (Default)

1: Transfer

All CR191-0 bits is transferred to CT191-0 bits when CTRAN bit changes “0” to “1”. The

transferred CT191-0 bits are valid after next block start signal is detected. CTRAN bit goes to

“0” after finishing the transfer.

EDIF1-0: Setting of audio interface mode in asynchronous mode. (See Table 30)

ECK1-0: Setting of EMCK input frequency (See Table 31)

MSEL: Master clock setting for TX in asynchronous mode (See Table 4)

MS0573-E-00

2006/12

- 56 -

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]