Data Sheet

AD9364

RX_FRAME Signal

SYNTHESIZERS

The device generates an RX_FRAME output signal whenever the

receiver outputs valid data. This signal has two modes: level

mode (RX_FRAME stays high as long as the data is valid) and

pulse mode (RX_FRAME pulses with a 50% duty cycle). Similarly,

the BBP must provide a TX_FRAME signal that indicates the

beginning of a valid data transmission with a rising edge. Similar

to the RX_FRAME signal, the TX_FRAME signal can remain

high throughout the burst or it can be pulsed with a 50% duty

cycle.

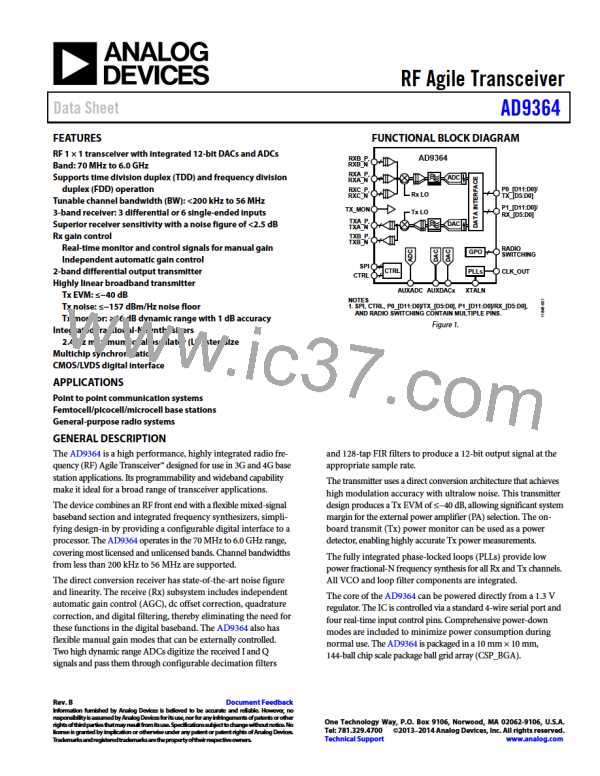

RF PLLs

The AD9364 contains two identical synthesizers to generate the

required LO signals for the RF signal paths—one for the receiver

and one for the transmitter. Phase-locked loop (PLL) synthesizers

are fractional-N designs incorporating completely integrated

voltage controlled oscillators (VCOs) and loop filters. In TDD

mode, the synthesizers turn on and off as appropriate for the Rx

and Tx frames. In FDD mode, the Tx PLL and the Rx PLL can

be activated at the same time. These PLLs require no external

components.

ENABLE STATE MACHINE

BB PLL

The AD9364 transceiver includes an enable state machine (ENSM)

that allows real-time control over the current state of the device.

The device can be placed in several different states during normal

operation, including

The AD9364 also contains a baseband PLL (BB PLL)

synthesizer that is used to generate all baseband related clock

signals. These include the ADC and DAC sampling clocks, the

DATA_CLK signal (see the Digital Data Interface section), and

all data framing signals. This PLL is programmed from 700 MHz

to 1400 MHz based on the data rate and sample rate requirements

of the system.

• Wait—power save, synthesizers disabled

• Sleep—wait with all clocks/BB PLL disabled

• Tx—Tx signal chain enabled

• Rx—Rx signal chain enabled

DIGITAL DATA INTERFACE

• FDD—Tx and Rx signal chains enabled

• Alert—synthesizers enabled

The AD9364 data interface uses parallel data ports (P0 and P1)

to transfer data between the device and the BBP. The data ports can

be configured in either single-ended CMOS format or differential

LVDS format. Both formats can be configured in multiple arrange-

ments to match system requirements for data ordering and data

port connections. These arrangements include single port data

bus, dual port data bus, single data rate, and double data rate.

The ENSM has two possible control methods: SPI control and

pin control.

SPI Control Mode

In SPI control mode, the ENSM is controlled asynchronously by

writing SPI registers to advance the current state to the next

state. SPI control is considered asynchronous to the DATA_CLK

because the SPI_CLK can be derived from a different clock

reference and can still function properly. The SPI control ENSM

method is recommended when real-time control of the

synthesizers is not necessary. SPI control can be used for real-

time control as long as the BBP has the ability to perform timed

SPI writes accurately.

Bus transfers are controlled using simple hardware handshake

signaling. The two ports can be operated in either bidirectional

(half-duplex) mode or in full duplex mode where half the bits

are used for transmitting data and half are used for receiving data.

The interface can also be configured to use only one of the data

ports for applications that do not require high data rates and

prefer to use fewer interface pins.

Pin Control Mode

DATA_CLK Signal

In pin control mode, the enable function of the ENABLE pin and

the TXNRX pin allow real-time control of the current state. The

ENSM allows TDD or FDD operation depending on the

configuration of the corresponding SPI register. The ENABLE

and TXNRX pin control method is recommended if the BBP

has extra control outputs that can be controlled in real time,

allowing a simple 2-wire interface to control the state of the

device. To advance the current state of the ENSM to the next

state, the enable function of the ENABLE pin can be driven by

either a pulse (edge detected internally) or a level.

The AD9364 supplies the DATA_CLK signal that the BBP uses

when receiving the data. The DATA_CLK signal can be set to a

rate that provides single data rate (SDR) timing where data is

sampled on each rising clock edge, or it can be set to provide

double data rate (DDR) timing where data is captured on both

rising and falling edges. SDR or DDR timing applies to

operation using either a single port or both ports.

FB_CLK Signal

For transmit data, the interface uses the FB_CLK signal as the

timing reference. FB_CLK allows source synchronous timing

with rising edge capture for burst control signals and either

rising edge (SDR mode) or both edge capture (DDR mode) for

transmit signal bursts. The FB_CLK signal must have the same

frequency and duty cycle as DATA_CLK.

When a pulse is used, it must have a minimum pulse width of

one FB_CLK cycle. In level mode, the ENABLE and TXNRX

pins are also edge detected by the AD9364 and must meet the

same minimum pulse width requirement of one FB_CLK cycle.

In FDD mode, the ENABLE and TXNRX pins can be remapped to

serve as real-time Rx and Tx data transfer control signals. In this

mode, the enable function of the ENABLE pin assumes the RXON

Rev. B | Page 29 of 32

ADI [ ADI ]

ADI [ ADI ]