EM73201

4-BIT MICRO-CONTROLLER FOR GENERAL PURPOSE PRODUCT

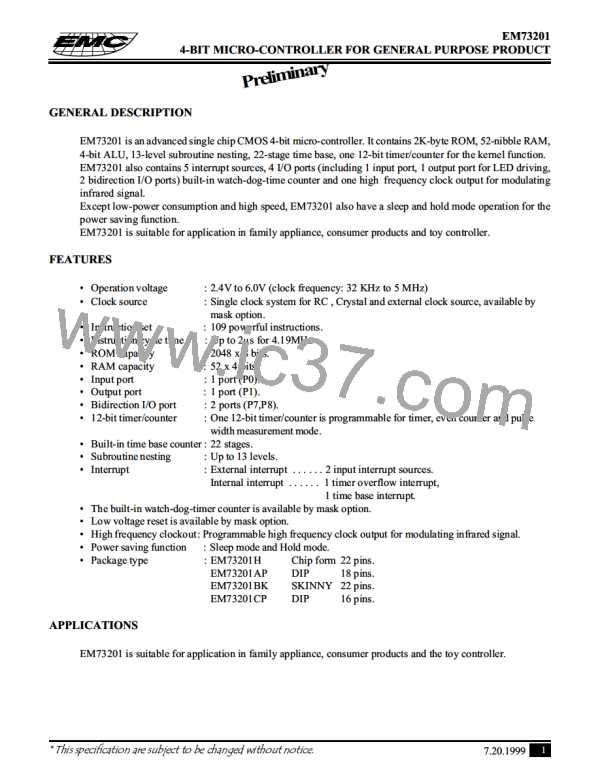

INSTRUCTION TABLE

(1) Data Transfer

Mnemonic

Object code ( binary ) Operation description

Byte

Cycle

Flag

C

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

Z

S

1

LDA

x

0110 1010 xxxx xxxx

0101 1010

Acc←RAM[x]

Acc ←RAM[HL]

Acc←ROM[DP]L

Acc←ROM[DP]H,DP+1

HR←k

LR←RAM[x],HR←RAM[x+1]

Acc←k

LR←k

RAM[x]←Acc

RAM[HL]←Acc

RAM[HL]←Acc, LR-1

RAM[HL]←Acc, LR+1

RAM[y]←k

RAM[HL]←k, LR+1

Acc←HR

Acc←LR

2

1

1

1

1

2

1

1

2

1

1

1

2

1

1

1

2

1

2

2

1

2

1

1

2

1

1

1

2

1

1

1

Z

Z

Z

Z

-

LDAM

LDAX

LDAXI

LDH

1

0110 0101

1

0110 0111

1

#k

1001 kkkk

1

LDHL x

0100 1110 xxxx xx00

1101 kkkk

-

1

LDIA #k

Z

-

1

LDL

#k

x

1000 kkkk

1

STA

0110 1001 xxxx xxxx

0101 1001

-

1

STAM

STAMD

STAMI

STD

-

1

0111 1101

Z

Z

-

C

C'

1

0111 1111

#k,y 0100 1000 kkkk yyyy

STDMI #k

THA

1010 kkkk

0111 0110

0111 0100

Z

Z

Z

C'

1

TLA

1

(2) Rotate

Mnemonic

Object code ( binary ) Operation description

Byte

Cycle

Flag

C

C

C

Z

Z

Z

S

RLCA

RRCA

0101 0000

0101 0001

←CF←Acc←

→CF→Acc→

1

1

1

1

C'

C'

(3) Arithmetic operation

Mnemonic

Object code ( binary ) Operation description

Byte

Cycle

Flag

C

C

-

Z

Z

Z

Z

Z

Z

Z

Z

Z

Z

Z

Z

S

ADCAM

ADD

0111 0000

#k,y 0100 1001 kkkk yyyy

Acc←Acc + RAM[HL] + CF

RAM[y]←RAM[y] +k

Acc←Acc+k

Acc←Acc + RAM[HL]

HR←HR+k

LR←LR+k

RAM[HL]←RAM[HL] +k

Acc←Acc-1

1

2

2

1

2

2

2

1

1

1

1

1

2

2

1

2

2

2

1

1

1

1

C'

C'

C'

C'

C'

C'

C'

C

ADDA #k

ADDAM

ADDH #k

ADDL #k

ADDM #k

DECA

0110 1110 0101 kkkk

0111 0001

-

-

0110 1110 1001 kkkk

0110 1110 0001 kkkk

0110 1110 1101 kkkk

0101 1100

-

-

-

-

DECL

DECM

0111 1100

0101 1101

LR←LR-1

RAM[HL]←RAM[HL] -1

Acc←Acc + 1

-

C

-

C

INCA

0101 1110

-

C'

* This specification are subject to be changed without notice.

7.20.1999 26

ELAN [ ELAN MICROELECTRONICS CORP ]

ELAN [ ELAN MICROELECTRONICS CORP ]