JMicron/JM20330

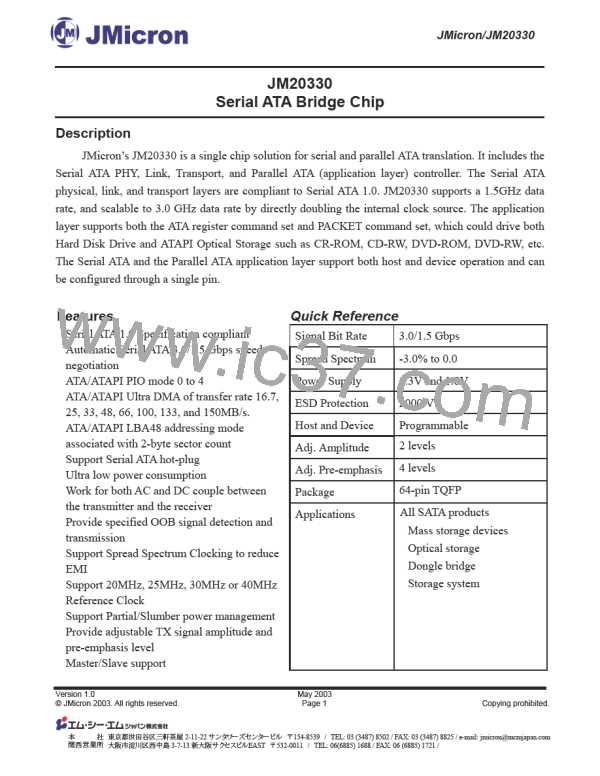

Functional Block Diagram

FIFO

FIFO

RXP/RXN

TXP/TXN

Physical

Layer

(PHY)

Transport

Layer

Link Layer

Application Layer (ATA/

ATAPI Controller)

Status and Control Register

(SCR)

MODE[2:0]

GIO0

GIO1

GPIO I/F

Register File

Fig. 1 Functional Block Diagram of JM20330

Applications

Device Bridge

Host Bridge

TXP/

TXN

RXP/

RXN

RXP/

RXN

TXP/

TXN

HDD/

Optical

Storage

PC IDE

Port

Parallel ATA

Parallel ATA

MODE

= 0xx

MODE

=1xx

Status and Control Register

(SCR)

Status and Control Register

(SCR)

GIO0

GIO1

GIO0

GIO1

GPIO I/

F

GPIO I/

F

Register File

Register File

JM30330

JM30330

Fig. 2 JM20330 Host and Device bridge system diagram

Product Information

Name

Description

JM20330

Serial ATA Bridge Chip

Design Kit

1 JM20330 Data Sheet

2 JM20330 Design Guide

Contact Information

Department

Sales

Email

sales@jmicron.com.tw

Application EVB

3

Tech. Support

fae@jmicron.com.tw

Version 1.0

© JMicron 2003. All rights reserved.

May 2003

Page 2

Copying prohibited.

本 社

関西営業所

東京都世田谷区三軒茶屋 2-11-22 サンタワーズセンタービルꢀ〒154-8539ꢀ/ꢀTEL: 03 (3487) 8502 / FAX: 03 (3487) 8825 / e-mail: jmicron@mcmjapan.com

大阪市淀川区西中島 3-7-13 新大阪サクセスビルEASTꢀ〒532-0011ꢀ/ꢀTEL: 06(6885) 1688 / FAX: 06 (6885) 1721 /

ETC [ ETC ]

ETC [ ETC ]