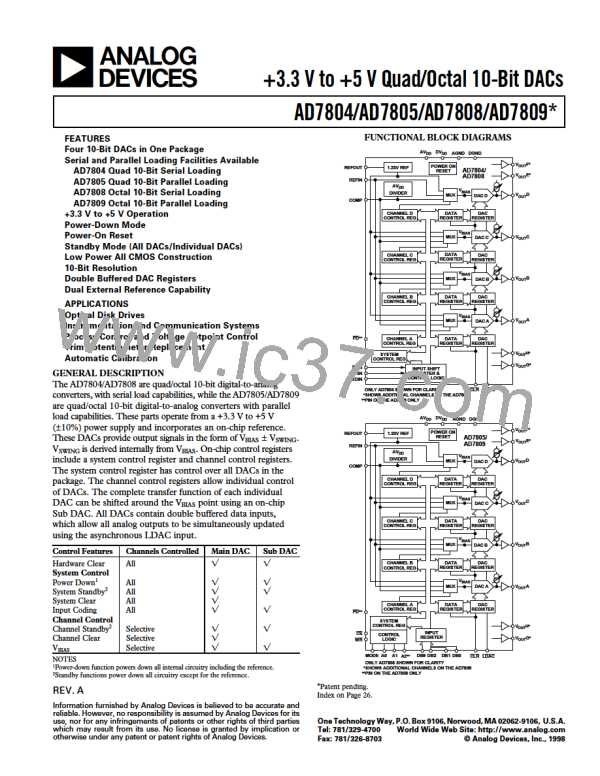

AD7804/AD7805/AD7808/AD7809

Table VI and Figure 22 show the analog outputs available for

the above configuration. The following is the procedure re-

quired if the complete transfer function needs to be offset

around the VBIAS point. Table VII and Figure 23 show the ana-

log output variations available from the Sub DAC.

OFFSET BINARY CODING

Table VIII shows the offset binary transfer function for the Main

DAC.

Table VIII. Offset Binary Code Table for Main DAC

Digital Inputs

MSB . . . LSB

Analog Output

System Control Register Write:

MODE = 0, address inputs (A2, A1, A0) are don’t cares.

1111111111

1111111110

1000000001

1000000000

0111111111

0000000001

0000000000

VBIAS+1.875 × VBIAS(1023–512)/1024

Write 020 Hex Configure part for 10-bit parallel, twos

complement coding, normal operation

VBIAS+1.875 × VBIAS(1022–512)/1024

VBIAS+1.875 × VBIAS/1024

VBIAS

VBIAS+1.875 × VBIAS(511–512)/1024

VBIAS+1.875 × VBIAS(1–512)/1024

VBIAS/16

Channel Control Register Write:

MODE = 0, address inputs (A2, A1, A0) select desired channel.

Write 091 Hex

Internal VDD/2 selected as VBIAS for

DAC, and any DAC data writes that

follow are to the Sub DAC.

NOTE: The span range is (30/16) × VBIAS = 1.875 × VBIAS

DAC Data Register Write:

31

V

BIAS

16

MODE = 1, address inputs (A2, A1, A0) select desired channel.

Write XX Hex

With MODE = 1 all data writes are to

the selected DACs Sub DAC. XX is the

required data. 7F Hex will give zero scale

and 80 Hex will give full scale from the

Sub DAC.

V

BIAS

Channel Control Register Write:

MODE = 0, address inputs (A2, A1, A0) select desired channel.

Write 011 Hex

Internal VDD/2 selected as VBIAS for

DAC, and any DAC data writes that

follow are to the Main DAC.

V

BIAS

16

DAC Data Register Write:

000 001

1FF

201

200

3FE 3FF

DAC INPUT CODE

MODE = 1, address inputs (A2, A1, A0) select desired channel.

Figure 25. Main DAC Output Voltage vs. DAC Input Codes

(HEX) for Offset Binary Coding

Write XXX Hex With MODE = 1 all data writes are to

the selected Main DAC. XXX is the

required data. 1FF Hex will give zero

scale and 200 Hex will give full scale

from the DAC.

Figure 25 shows the Main DAC transfer function when offset

binary coding is used. With offset binary coding selected the

output voltage can be calculated as follows:

V

OUT' = VBIAS + 1.875 × VBIAS × ((NA-512)/1024)

where NA is the decimal equivalent of the offset binary input

code. NA ranges from 0 to 1023.

Table IX shows the offset binary transfer function for the Sub

DAC. Figure 26 shows the Sub DAC transfer function for

offset binary coding. Any Sub DAC output voltage can be

expressed as:

V

OUT" = VBIAS/16 × [(NB-128)/256]

where NB is the decimal equivalent of the offset binary input

code. NB ranges from 0 to 255.

–18–

REV. A

ETC [ ETC ]

ETC [ ETC ]