XC9536 In-System Programmable CPLD

V

TEST

R

1

Output Type

V

V

R

R

C

L

CCIO

TEST

1

2

Device Output

5.0 V

3.3 V

5.0 V

3.3 V

160 Ω

260 Ω

120 Ω

360 Ω

35 pF

35 pF

R

C

L

2

X5906

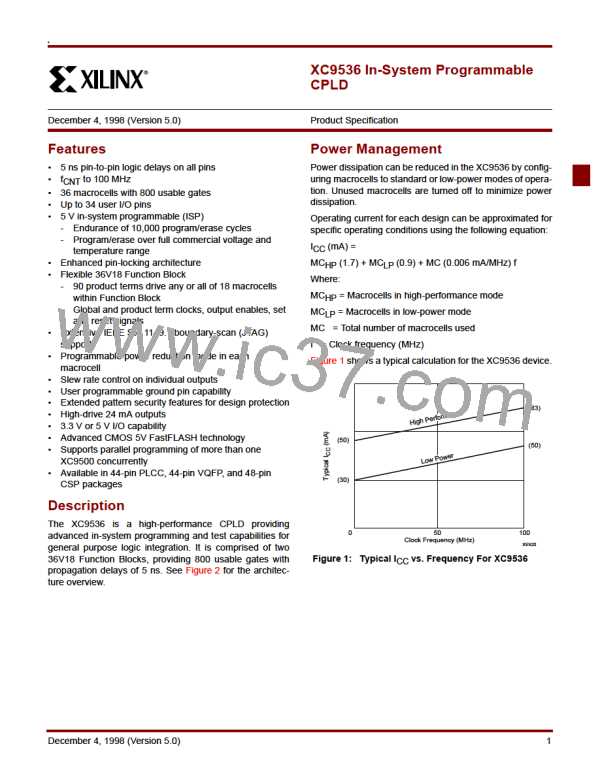

Figure 3: AC Load Circuit

Internal Timing Parameters

XC9536-5 XC9536-6 XC9536-7 XC9536-10 XC9536-15

Min Max Min Max Min Max Min Max Min Max

Symbol

Parameter

Units

Buffer Delays

t

t

t

t

t

t

Input buffer delay

GCK buffer delay

1.5

1.5

4.0

5.0

2.0

0.0

1.5

1.5

4.0

5.0

2.0

0.0

2.5

1.5

4.5

5.5

2.5

0.0

3.5

2.5

6.0

6.0

3.0

0.0

4.5

3.0

7.5

ns

ns

ns

IN

GCK

GSR

GTS

OUT

EN

GSR buffer delay

GTS buffer delay

11.0 ns

Output buffer delay

4.5

0.0

ns

ns

Output buffer enable/disable delay

Product Term Control Delays

t

t

t

Product term clock delay

Product term set/reset delay

Product term 3-state delay

3.0

1.0

5.5

3.0

1.0

5.5

3.0

2.0

4.5

3.0

2.5

3.5

2.5

3.0

5.0

ns

ns

ns

PTCK

PTSR

PTTS

Internal Register and Combinatorial delays

t

t

t

t

t

t

t

Combinatorial logic propagation delay

Register setup time

0.5

1.5

0.5

1.0

3.0

ns

ns

ns

ns

ns

ns

ns

PDI

SUI

HI

2.5

1.0

2.5

1.0

1.5

3.0

2.5

3.5

3.5

4.5

Register hold time

Register clock to output valid time

Register async. S/R to output delay

0.5

6.0

0.5

6.0

0.5

6.5

0.5

7.0

0.5

8.0

COI

AOI

RAI

LOGI

Register async. S/R recovery before clock 5.0

Internal logic delay

5.0

7.5

10.0

10.0

1.0

9.0

1.0

9.0

2.0

2.5

3.0

tLOGILP Internal low power logic delay

10.0

11.0

11.5 ns

Feedback Delays

t

FastCONNECT matrix feeback delay

6.0

6.0

8.0

9.5

11.0 ns

F

Time Adders

3

t

t

Incremental Product Term Allocator delay

Slew-rate limited delay

0.8

3.5

0.8

3.5

1.0

4.0

1.0

4.5

1.0

5.0

ns

ns

PTA

SLEW

Note: 3. tPTA is multiplied by the span of the function as defined in the family data sheet.

December 4, 1998 (Version 5.0)

5

XILINX [ XILINX, INC ]

XILINX [ XILINX, INC ]