TPS7H5005-SEP, TPS7H5006-SEP, TPS7H5007-SEP, TPS7H5008-SEP

www.ti.com

SLVSGG1 – FEBRUARY 2022

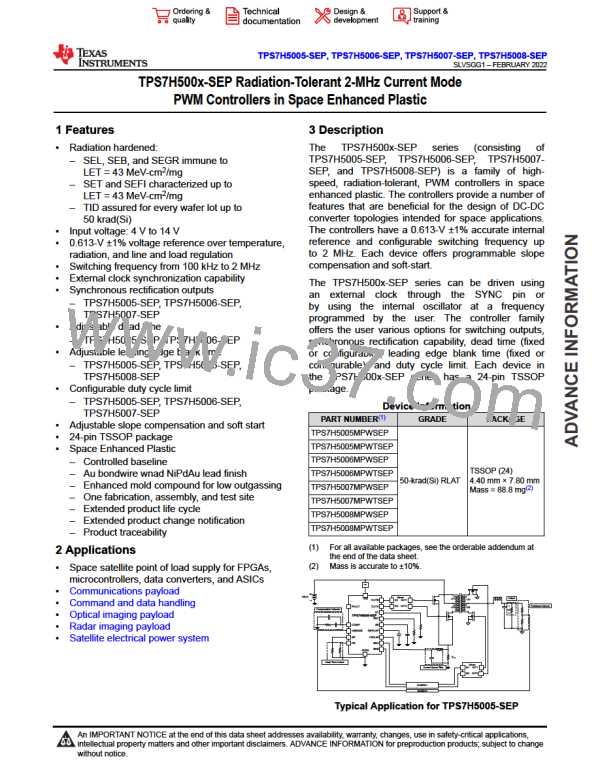

8.2 Functional Block Diagram

10

11

14

15

Over

Temperature

24 COMP

EN_INT

PWM_OUT

OCP

3.55V/3.4V

VLDO

+

-

↓

UVLO

EN

Switching Logic

VIN

EN

9

8

CLK

SS

22

+

+

VIN

EA

OCP

EN Detect

-

23 VSENSE

VREF

Ready

Voltage Ref.

COMP

VREF

REFCAP 20

COMPOV2

1/CCSR

+

-

SSPD

+

-

CS_ILIM 18

Current Limit

VIN

1.05V

Hiccup

Timer

HICC

5

BG/LDO

17

7

VLDO

DCL

+

-

19

FAULT

Fault

Timer

AVDD

VLDO

0.6V/0.5V

SP

PS

RT

3

2

1

Deadtime

RT Bias

SYNC OUT EN

Slope

Comp

16 AVSS

SYNC

Detect

SYNC/CLK

6

OSC

21

12

13

4

Figure 8-1. TPS7H5005-SEP Functional Block Diagram

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

25

Product Folder Links: TPS7H5005-SEP TPS7H5006-SEP TPS7H5007-SEP TPS7H5008-SEP

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]