TPS56C231

ZHCSNT8 –AUGUST 2022

www.ti.com.cn

7.3 特性说明

7.3.1 PWM 运行和D-CAP3 控制模式

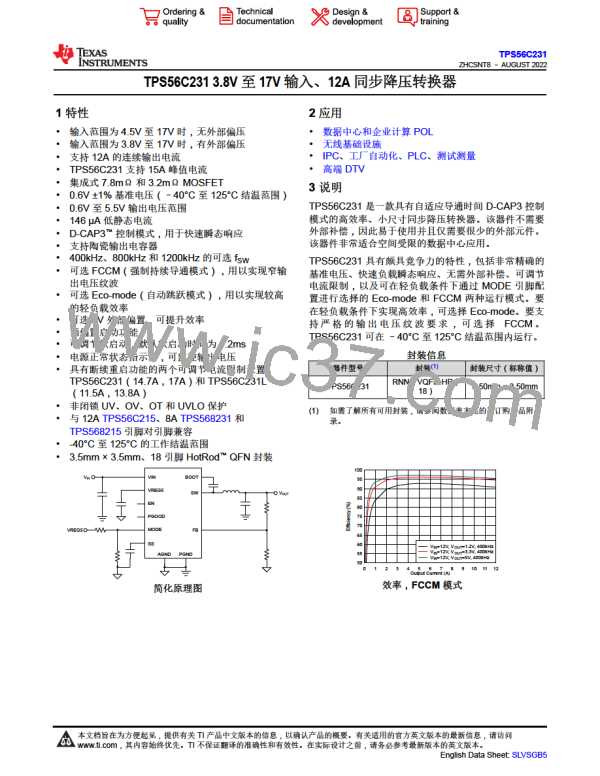

TPS56C231x 使用自适应导通时间 PWM 控制及专有 D-CAP3 控制模式运行,该模式可实现较少的外部元件数量

以及快速负载瞬态响应,同时保持良好的输出电压精度。在每个开关周期开始时,高侧MOSFET 都会在内部一次

性计时器设置的导通时间内导通。该导通时间是根据转换器的输入电压、转换器的输出电压和伪固定频率设置

的,因此,这种类型的控制拓扑称为自适应导通时间控制。在反馈电压 (VFB) 降至低于内部基准电压 (VREF) 后,

一次性计时器复位并再次开启。产生的输出斜坡将馈送到 FB 引脚来模拟输出电压纹波,因此能够支持使用 ESR

非常低的输出电容器,例如多层陶瓷电容器 (MLCC)。D-CAP3 控制模式拓扑不需要外部电流检测网络或环路补

偿。

TPS56C231x 包含一个误差放大器,可使输出电压变得非常准确。该误差放大器在其他类型的 D-CAP3 控制模式

中不存在。对于任何内部补偿的控制拓扑,它可以支持一系列输出滤波器。与 TPS56C231x 配合使用的输出滤波

器是低通L-C 电路。此L-C 滤波器具有方程式1 中所示的双极点。

1

¦

=

P

2´ p´ LOUT ´ COUT

(1)

在低频率下,整体环路增益是由输出设定点电阻分压器网络和TPS56C231x 的内部增益设定的。低频L-C 双极点

具有 180 度同相压降。在输出滤波器频率下,增益以每十倍频程 –40dB 的速率滚降,且相位快速下降。内部纹

波生成网络引入了高频零点,可将增益滚降从每十倍频程 –40dB 降低到 –20dB,并将相位增加到零点频率之上

每十倍频程90°。内部纹波注入高频零点根据所选的开关频率进行更改,如表7-1 所示。为输出滤波器选择的电感

器和电容器必须确保双极位置足够靠近高频零点,以便由该高频零点提供的相位提升可提供足够的相位裕度来满

足稳定性要求。整个系统的交叉频率通常必须低于开关频率(fSW) 的五分之一。

表7-1. 纹波注入零点

开关频率(kHz)

零点位置(kHz)

400

800

17.8

27.1

29.8

1200

7.3.2 Eco-mode 控制

TPS56C231x 采用 Eco-mode 控制设计,可提高轻负载条件下的效率。可以使用 MODE 引脚选择此选项,如表

7-2 所示。当输出电流随着重负载条件降低时,电感器电流也会降低。如果输出电流减小到足够程度,电感器电流

的谷值将达到零电平,这是连续导通模式和不连续导通模式之间的边界。当检测到电感器电流为零时,低侧

MOSFET 会关断。随着负载电流进一步降低,转换器会进入不连续导通模式。导通时间与连续导通模式下的导通

时间大致相同。关断时间会增加,因为在负载电流较小时对输出进行放电需要更长时间。使用方程式 2 可计算转

换到Eco-mode 运行状态时的轻负载电流(IOUT(LL))。

(V -VOUT ) × VOUT

1

IN

IOUT(LL)

=

×

2 × LOUT × FSW

V

IN

(2)

确定应用要求后,在设计中采用的输出电感 (LOUT),应使电感器峰峰值纹波电流大约介于 IOUT(max)(应用中的峰

值电流)的20% 与30% 之间。适当调整电感器的大小,使谷值电流不会达到负低侧电流限值。

7.3.3 4.7V LDO

VREG5 引脚是内部4.7V 线性稳压器的输出,为所有内部电路和MOSFET 栅极驱动器产生偏置。必须使用4.7µF

电容器将 VREG5 引脚旁路掉。高于 LDO 内部输出电压的外部电压可以覆盖内部 LDO,在检测到更高电压后将

其切换至外部电源轨。此操作可以提高转换器的效率,因为静态电流现在从这个外部电源轨而不是从输入电源流

出。UVLO 电路监测 VREG5 引脚电压,并在 VREG5 降至低于 UVLO 阈值时禁用输出。在 VREG5 电源轨上使

用外部偏置时,可以采用任何上电和断电时序,但必须了解的是,如果 VREG5 电源轨上有放电路径可以从

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

15

Product Folder Links: TPS56C231

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]