OPA189, OPA2189

www.ti.com.cn

ZHCSH15A –SEPTEMBER 2017–REVISED NOVEMBER 2017

11 布局

11.1 布局指南

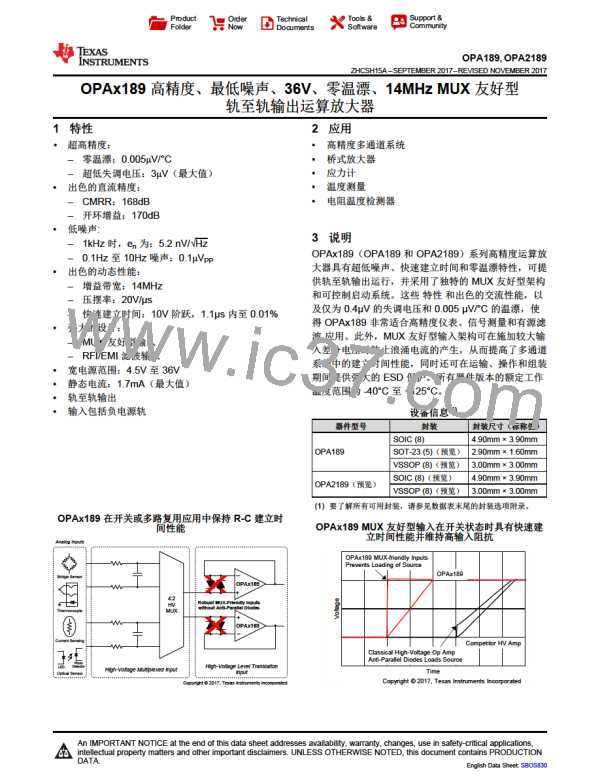

为了实现器件的最佳运行性能,应使用良好的 PCB 布局规范,包括:

•

噪声可通过全部电路电源引脚及运算放大器本身传入模拟电路。旁路电容器通过提供模拟电路的本地低阻抗

电源来减少耦合噪声。

–

在每个电源引脚和接地端之间连接低 ESR 0.1µF 陶瓷旁路电容器,放置位置尽量靠近器件。从 V+ 到接

地端的单个旁路电容器适用于单通道电源 应用。

•

•

将电路的模拟和数字部分单独接地是最简单和最有效的噪声抑制方法之一。多层 PCB 中通常将一层或多层

专门作为接地层。接地层有助于散热和降低电磁干扰 (EMI) 噪声。确保对数字接地和模拟接地进行物理隔

离,同时应注意接地电流。有关更多详细信息,请参阅 PCB 是一个运算放大器设计的组件。

为了减少寄生耦合,请让输入走线尽可能远离电源走线或输出走线。如果这些走线不能保持分离,让敏感走

线与有噪声的走线垂直相交要比平行相交好得多。

•

•

•

•

•

外部组件的位置应尽量靠近器件。如图 52 所示,使 RF 和 RG 接近反相输入可最大限度地减小寄生电容。

尽可能缩短输入走线。切记:输入走线是电路中最敏感的部分。

考虑在关键走线周围设定驱动型低阻抗保护环。这样可显著减少附近走线在不同电势下产生的泄漏电流。

为获得最佳性能,TI 建议在组装 PCB 板后对其进行清洁。

任何精密集成电路都可能因湿气渗入塑料封装中而出现性能变化。请遵循所有的 PCB 水清洁流程,TI 建议

将 PCB 组装烘干,以去除清洁时渗入器件封装中的湿气。大多数情形下,清洗后在 85°C 下低温烘干 30

分钟即可。

11.2 布局示例

Place bypass

capacitors as close to

device as possible

(avoid use of vias)

Use ground pours for

shielding the input

signal pairs

GND

C3

C4

+V

R3

C3

C4

R3

INœ

+V

1

NC

œIN

+IN

Vœ

NC

V+

8

7

6

5

1

2

3

4

NC

œIN

+IN

Vœ

NC

V+

8

7

6

5

R1

R1

2

3

4

INœ

œ

OUT

IN+

R2

OUT

NC

OUT

OUT

NC

+

R2

-V

C1

C2

IN+

R4

GND

R4

-V

Place components

C1

C2

Use a low-

ESR,ceramic bypass

capacitor

close to device and to

each other to reduce

parasitic errors

Copyright © 2017, Texas Instruments Incorporated

图 52. 差分放大器配置的运算放大器电路板布局

版权 © 2017, Texas Instruments Incorporated

31

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]