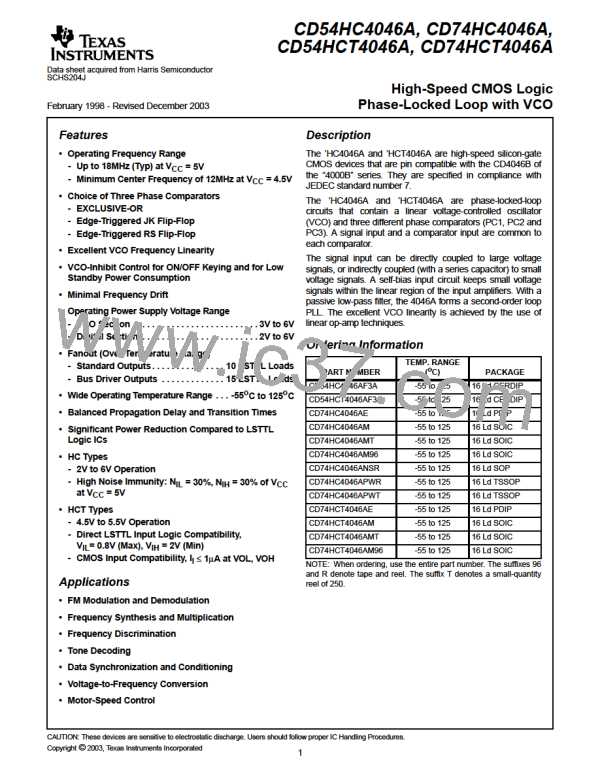

CD54HC4046A, CD74HC4046A, CD54HCT4046A, CD74HCT4046A

PHASE

SUBJECT

COMPARATOR

DESIGN CONSIDERATIONS

o

PLL Conditions with

No Signal at the

SIG Input

IN

PC1

PC2

PC3

VCO adjusts to f with φDEMOUT = 90 and V

= 1/2 V

(see Figure 2)

o

VCOIN

CC

o

VCO adjusts to f

VCO adjusts to f

with φDEMOUT = -360 and V

= 0V (see Figure 4)

MIN

VCOIN

VCOIN

o

with φDEMOUT = 360 and V

= V

(see Figure 6)

MAX

CC

PLL Frequency

Capture Range

PC1, PC2 or PC3 Loop Filter Component Selection

|F

|

)

(j

ω

R3

-1/

τ

C2

INPUT

OUTPUT

ω

(B) AMPLITUDE CHARACTERISTIC

(C) POLE-ZERO DIAGRAM

(A) τ = R3 x C2

1/2

A small capture range (2f ) is obtained if τ > 2f ≈ 1/π (2πf /τ.)

c

c

L

FIGURE 46. SIMPLE LOOP FILTER FOR PLL WITHOUT OFFSET

R3

|F

|

)

(j

ω

R4

m =

R4

C2

R3 + R4

INPUT

OUTPUT

-1/

-1/

3

2

τ

τ

m

1/

1/

2

ω

3

τ

τ

(B) AMPLITUDE CHARACTERISTIC

(C) POLE-ZERO DIAGRAM

(A) τ1 = R3 x C2;

τ2 = R4 x C2;

τ3 = (R3 + R4) x C2

FIGURE 47. SIMPLE LOOP FILTER FOR PLL WITH OFFSET

PLL Locks on

Harmonics at Center

Frequency

PC1 or PC3

PC2

Yes

No

Noise Rejection at

Signal Input

PC1

High

Low

PC2 or PC3

PC1

o

AC Ripple Content

when PLL is Locked

f = 2f , large ripple content at φDEMOUT = 90

r i

o

PC2

f = f , small ripple content at φDEMOUT = 0

r i

o

PC3

f = fSIG , large ripple content at φDEMOUT = 180

IN

r

20

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]